### Space Transformer Organic Technologies for Next-Generation Probe Card Substrates

# FICT

**Yo Nozaka** FICT LIMITED

# Outline

### Introduction

- Background

- Demand for Probe Card

- Manufacturing Structure Selection

- Goals/Challenges

### Latest Development Status of Space Transformer Organic

- TOPIC 1 : Pin Count Increase (Multi-DUTs)

- TOPIC 2 : Fine Pitch Development

- Future Challenges

### Breakthrough Technology : G-ALCS (Multi Layer Glass Substrate)

- What is G-ALCS?

- Characteristics of G-ALCS

- Our Technology Roadmap

- Conclusion

Yo Nozaka

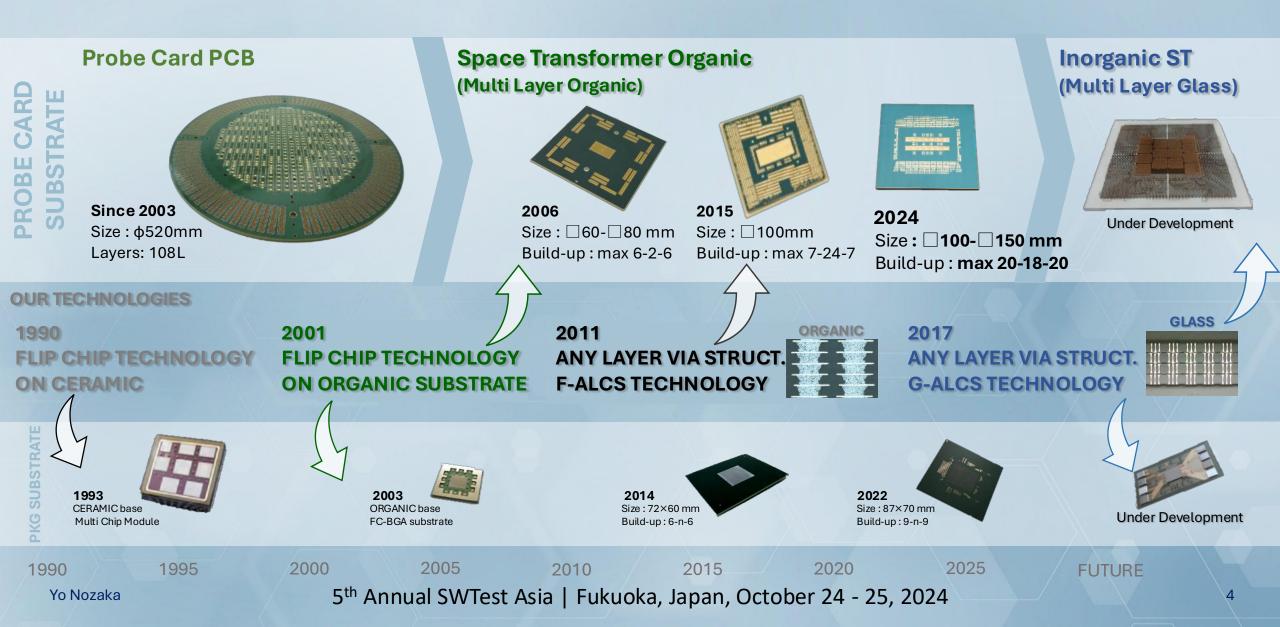

# **Evolution of FICT Probe Card Substrates**

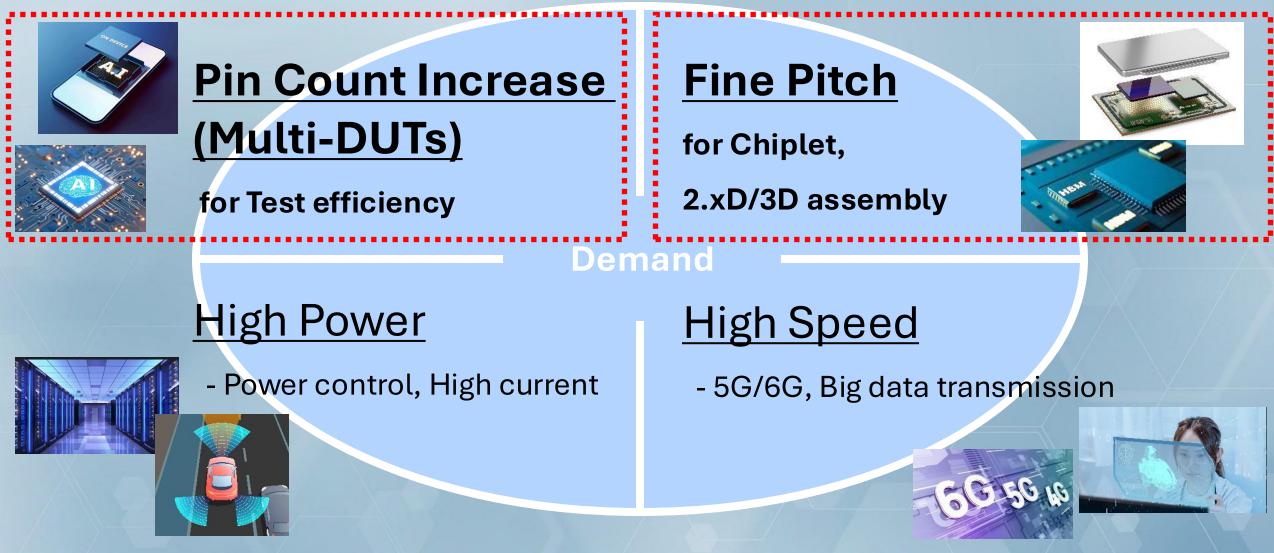

# **Demand for Probe Card**

Yo Nozaka

# **Manufacturing Structure Selection**

| Specifications                 |      | Build up                                             |           | Thin film                  |

|--------------------------------|------|------------------------------------------------------|-----------|----------------------------|

| High density                   | Good |                                                      | Excellent |                            |

| Layer #                        | Good | <u>Core + Build up</u>                               | Poor      | Core + Thin film           |

| Electrical properties (SI, PI) | Good |                                                      | Poor      |                            |

| Power delivery structure       | Good | Build up<br>Core                                     | Poor      | Thin film                  |

| Productivity                   | Good | Build up                                             | Poor      |                            |

| Cost (NRE, Material, Yield)    | Good |                                                      | Poor      |                            |

| Lead time                      | Fair |                                                      | Fair      |                            |

| Comments                       |      | rally superior properties<br>critical disadvantages) | Superi    | or on high density routing |

Build up structure can be applied to a wide range of existing products. By unleashing its potential, we aim to offer higher-performance products.

Yo Nozaka

# **Goals/Challenges**

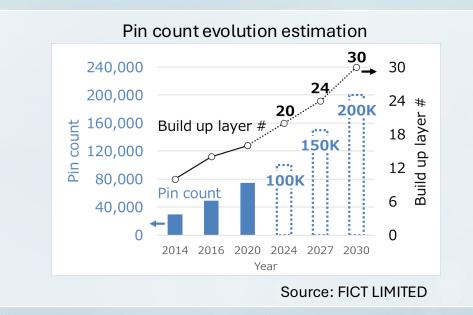

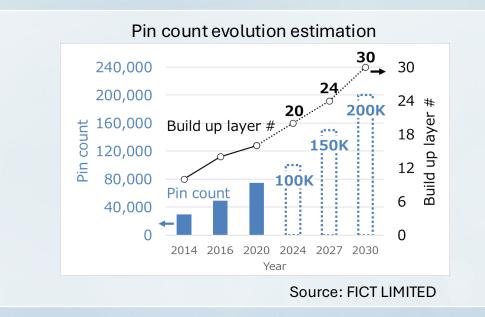

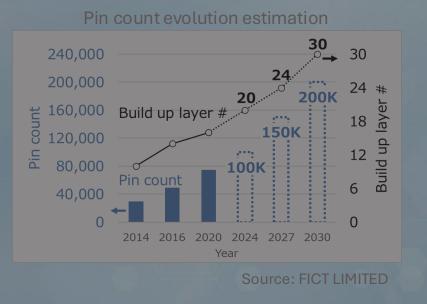

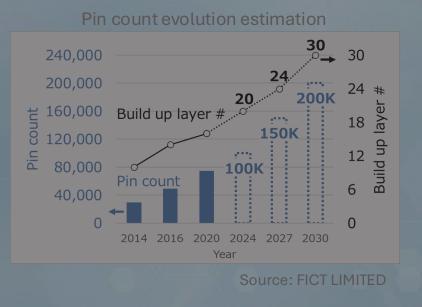

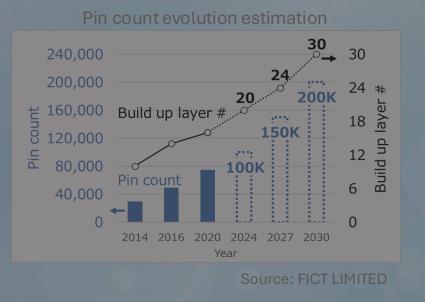

### **TOPIC 1** Pin Count Increase (Multi-DUTs)

### <u>Goal : 100K pins by 2024</u> <u>200K pins by 2030</u>

#### Challenge :

Increasing build up layers up to 20 and more

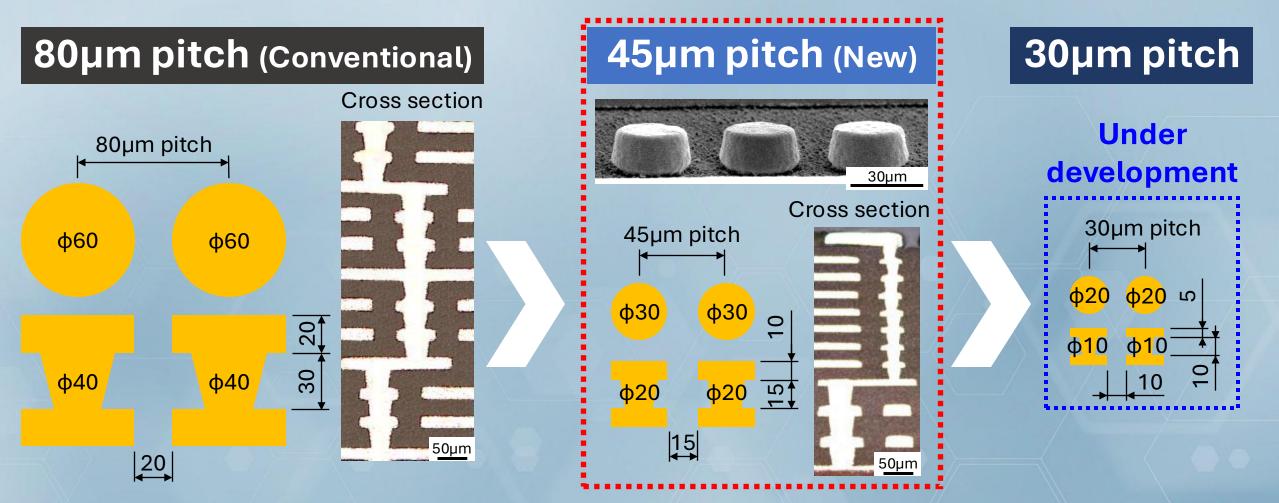

### TOPIC 2 Fine Pitch Development

### <u>Goal : 45µm pitch by 2024</u> <u>30µm pitch by 2026</u>

Min. Bump pitch scale roadmap for chiplet interposer

|                       |      |      |      |      | (unit:µm) |

|-----------------------|------|------|------|------|-----------|

| Material              | 2019 | 2022 | 2025 | 2028 | 2031      |

| Organic<br>interposer | 50   | 45   | 40   | 40   | 30        |

| Silicon<br>interposer | 40   | 35   | 30   | 20   | 20        |

Source: Heterogeneous Integration Roadmap. IEEE

### **Challenges:**

- 1. Fine via pitch by using thin build up structure

- 2. Pad position control by lowering substrate CTE

Yo Nozaka

# **Goals/Challenges**

### **TOPIC 1** Pin Count Increase (Multi-DUTs)

### <u>Goal : 100K pins by 2024</u> <u>200K pins by 2030</u>

#### Challenge :

Increasing build up layers up to 20 and more

**TOPIC 2** Fine Pitch Development

### <u>Goal : 45µm pitch by 2024</u> <u>30µm pitch by 2026</u>

Min. Bump pitch scale roadmap for chiplet interposer

|                       |      |      |      |      | (unit:µm) |

|-----------------------|------|------|------|------|-----------|

| Material              | 2019 | 2022 | 2025 | 2028 | 2031      |

| Organic<br>interposer | 50   | 45   | 40   | 40   | 30        |

| Silicon<br>interposer | 40   | 35   | 30   | 20   | 20        |

Source: Heterogeneous Integration Roadmap. IEEE

### **Challenges :**

- 1. Fine via pitch by using thin build up structure

- 2. Pad position control by lowering substrate CTE

Yo Nozaka

TOPIC 1: Pin Count Increase (Multi-DUTs)

### Approach to Keep up with Pin Count Increasing Trend

|        | Pin count increasing                                   |               |                                                                            |     |                                    |  |                                              |

|--------|--------------------------------------------------------|---------------|----------------------------------------------------------------------------|-----|------------------------------------|--|----------------------------------------------|

|        | I/O nets increasing                                    |               |                                                                            |     |                                    |  |                                              |

|        | Routing area increasing                                |               |                                                                            |     |                                    |  |                                              |

|        | High build up layers                                   | S             | Lar<br>As                                                                  |     | Size<br>18LY PROCESS               |  | Fine L/S                                     |

|        | Essential technologies                                 | to increas    | e build up l                                                               | ay  | ers                                |  |                                              |

|        | Technology 1                                           | Techr         | nology 2                                                                   |     | Technology 3                       |  | Technology 4                                 |

|        | Laser via stress<br>reduction by small CTE<br>mismatch | process tur   | Laser via shape imp. by<br>process tuning (Laser<br>via drilling, Desmear) |     | Flat dielectric/Cu plating surface |  | Layer to layer position accuracy improvement |

|        | Main focus in this present                             | ation         |                                                                            |     |                                    |  |                                              |

| Nozaka | 5 <sup>th</sup> Ann                                    | ual SWTest As | sia   Fukuoka,                                                             | Jap | an, October 24 - 25, 2024          |  | 9                                            |

Yo

TOPIC 1: Pin Count Increase (Multi-DUTs)

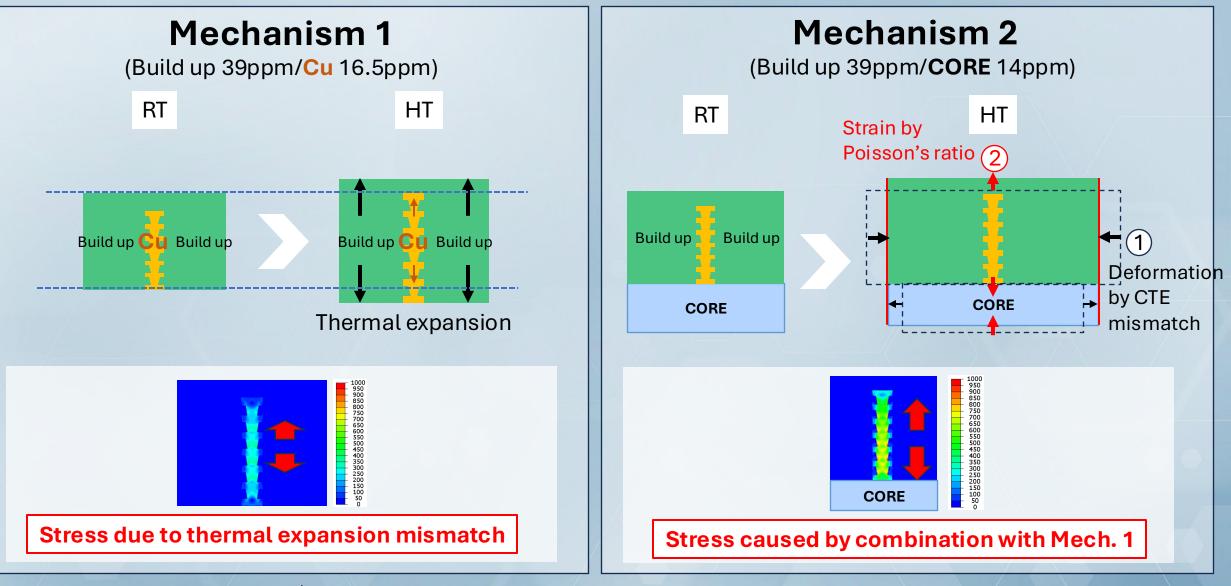

# **Thermal stress due to CTE mismatch**

5<sup>th</sup> Annual SWTe

Yo Nozaka

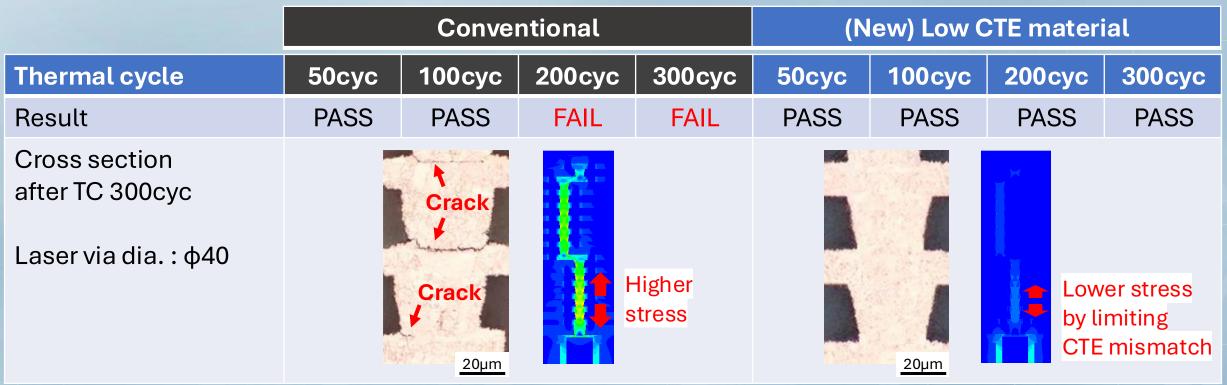

### Test Vehicle Specification (Increasing Build up Layers)

| Specifications          |               | Conventional |           |      | (New) Low CTE material |         |        |

|-------------------------|---------------|--------------|-----------|------|------------------------|---------|--------|

| Subs                    | trate size    | 100mm        | 1*100mm*3 | mmt  | 100mi                  | m*100mm | n*3mmt |

| La                      | ayers         |              | 20-8-20   |      |                        | 20-8-20 |        |

|                         | Core          | ⊿ 25 -       | 14        | -57  | %                      | ך 6     | . 14   |

| CTE<br>[ppm]            | Build up film |              | 39        | -49  | %                      | 20      | 214    |

| The best of             | Copper        | ⊿ 22.5 -     | 16.5      |      | ,                      | 16.5    | -⊿3.5  |

|                         | Core          |              | 26.5      | +28  | 3%                     | 34      |        |

| Modulus<br>[GPa]        | Build up film |              | 5         | +16  | 0%                     | 13      |        |

|                         | Copper        |              | 130       |      |                        | 130     |        |

| Build up film thickness |               | 30µm         |           | 30µm |                        |         |        |

| Laser via diameter      |               | 40µm         |           | 40µm |                        |         |        |

| DUT pad diameter        |               | 60µm         |           | 60µm |                        |         |        |

| DU                      | Tpitch        |              | 80µm      |      | 80µm                   |         |        |

Yo Nozaka

5<sup>th</sup> Annual SWTest Asia | Fukuoka, Japan, October 24 - 25, 2024

TOPIC 1: Pin Count Increase (Multi-DUTs)

# **Results (Thermal Cycle Test)**

### Test condition : Reflow 235deg.C x 6times + TC 50, 100, 200, 300cycles

Reliability was improved by controlling CTE mismatch among Cu/Build up/Core. 100K pins structure with 20 build up layers is in mass production.

Yo Nozaka

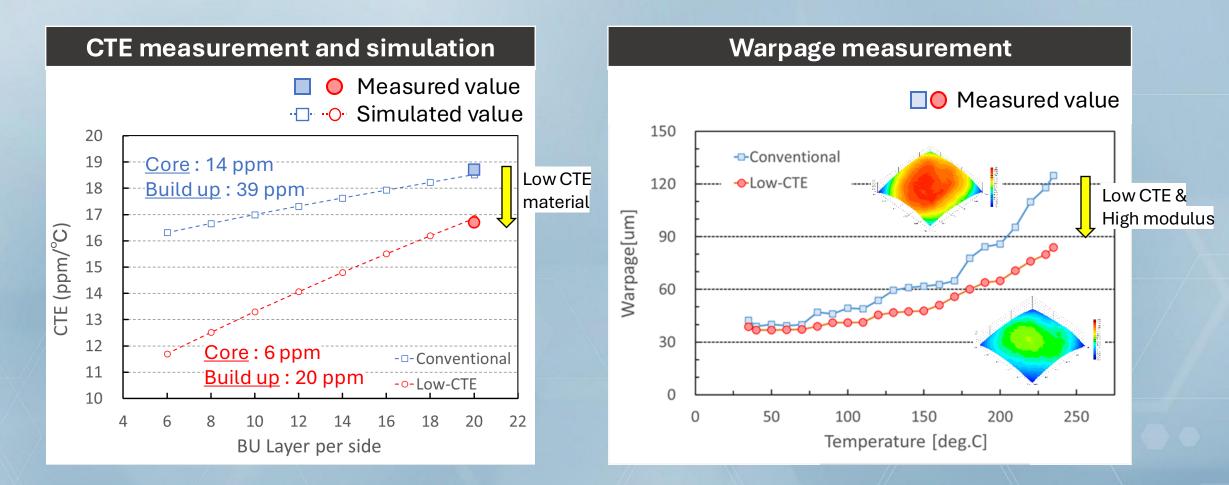

TOPIC 1: Pin Count Increase (Multi-DUTs)

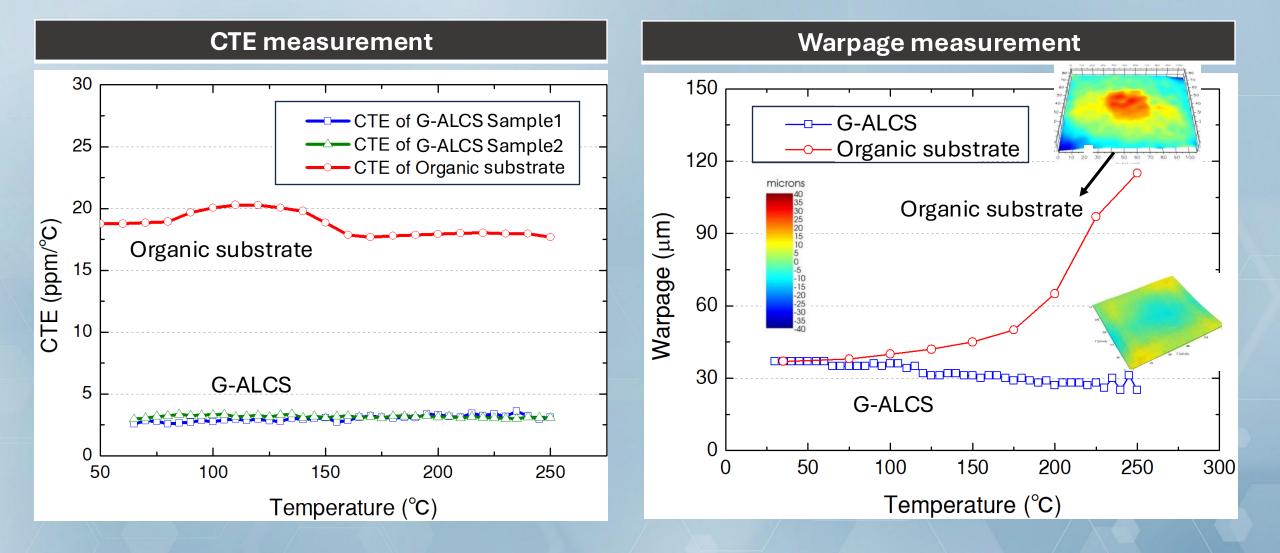

# **Results (CTE and Warpage)**

CTE and warpage was improved by applying low CTE material set.

Yo Nozaka

# **Goals/Challenges**

### **TOPIC 1** Pin Count Increase (Multi-DUTs)

### <u>Goal : 100K pins by 2024</u> <u>200K pins by 2030</u>

**Challenge :** Increasing build up layers up to 20 and more

### TOPIC 2 Fine Pitch Development

### <u>Goal : 45µm pitch by 2024</u> <u>30µm pitch by 2026</u>

Min. Bump pitch scale roadmap for chiplet interposer

|                       |      |      |      |      | (unit:µm) |

|-----------------------|------|------|------|------|-----------|

| Material              | 2019 | 2022 | 2025 | 2028 | 2031      |

| Organic<br>interposer | 50   | 45   | 40   | 40   | 30        |

| Silicon<br>interposer | 40   | 35   | 30   | 20   | 20        |

Source: Heterogeneous Integration Roadmap. IEEE

### **Challenges:**

- 1. Fine via pitch by using thin build up structure

- 2. Pad position control by lowering substrate CTE

Yo Nozaka

# **Goals/Challenges**

### **TOPIC 1** Pin Count Increase (Multi-DUTs)

### <u>Goal : 100K pins by 2024</u> <u>200K pins by 2030</u>

Challenge : Increasing build up layers up to 20 and more

### TOPIC 2 Fine Pitch Development

### <u>Goal : 45µm pitch by 2024</u> <u>30µm pitch by 2026</u>

Min. Bump pitch scale roadmap for chiplet interposer

|                       |      |      |      |      | (unit:µm) |

|-----------------------|------|------|------|------|-----------|

| Material              | 2019 | 2022 | 2025 | 2028 | 2031      |

| Organic<br>interposer | 50   | 45   | 40   | 40   | 30        |

| Silicon<br>interposer | 40   | 35   | 30   | 20   | 20        |

Source: Heterogeneous Integration Roadmap. IEEE

### **Challenges:**

- 1. Fine via pitch by using thin build up structure

- 2. Pad position control by lowering substrate CTE

Yo Nozaka

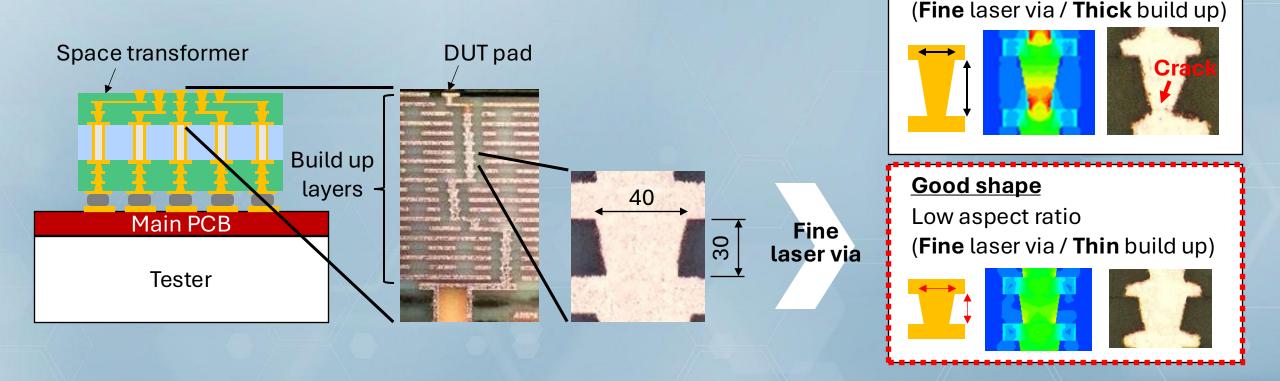

**Bad shape**

High aspect ratio

### Challenge 1 : Fine Via Pitch by Using Thin Build up Structure

### For fine pitch laser, control of aspect ratio (laser via/build up thickness) is important.

Yo Nozaka

TOPIC 2: Fine Pitch Development

### Test Vehicle Specification (Challenge 1 : Fine Via Pitch)

| Specifications             |               | Conventional build u<br>& Low CTE material | p (New) Thin build up<br>& Low CTE material |

|----------------------------|---------------|--------------------------------------------|---------------------------------------------|

| Substrate size             |               | 72mm*72mm*3mmt                             | 72mm*72mm*3mmt                              |

| L                          | ayers         | 16-8-16                                    | 16-8-16                                     |

| OTE                        | Core          | 6                                          | 6                                           |

| CTE<br>[ppm] Build up film |               | 20                                         | 20                                          |

| Copper                     |               | 16.5                                       | 16.5                                        |

|                            | Core          | 34                                         | 34                                          |

| Modulus<br>[GPa]           | Build up film | 13                                         | 13                                          |

| [010]                      | Copper        | 130                                        | 130                                         |

| Build up f                 | ilm thickness | 30µm                                       | 15µm                                        |

| Laser via diameter         |               | 40µm                                       | -50% 20μm                                   |

| DUT pa                     | id diameter   | 60µm                                       | 30µm                                        |

| DU                         | IT pitch      | 80µm 📃                                     | -44% 45µm                                   |

Yo Nozaka

**TOPIC 2: Fine Pitch Development**

# **Results (Challenge 1 : Fine Via Pitch)**

### $45\mu m$ pitch with $\phi 20\mu m$ laser via was developed by using thin build up structure.

Yo Nozaka

# **Goals/Challenges**

### **TOPIC 1** Pin Count Increase (Multi-DUTs)

### <u>Goal : 100K pins by 2024</u> <u>200K pins by 2030</u>

**Challenge :** Increasing build up layers up to 20 and more

### TOPIC 2 Fine Pitch Development

### <u>Goal : 45µm pitch by 2024</u> <u>30µm pitch by 2026</u>

Min. Bump pitch scale roadmap for chiplet interposer

|                       |      |      |      |      | (unit:µm) |  |

|-----------------------|------|------|------|------|-----------|--|

| Material              | 2019 | 2022 | 2025 | 2028 | 2031      |  |

| Organic<br>interposer | 50   | 45   | 40   | 40   | 30        |  |

| Silicon<br>interposer | 40   | 35   | 30   | 20   | 20        |  |

Source: Heterogeneous Integration Roadmap. IEEE

#### **Challenges:**

I. Fine via pitch by using thin build up structure

2. Pad position control by lowering substrate CTE

Yo Nozaka

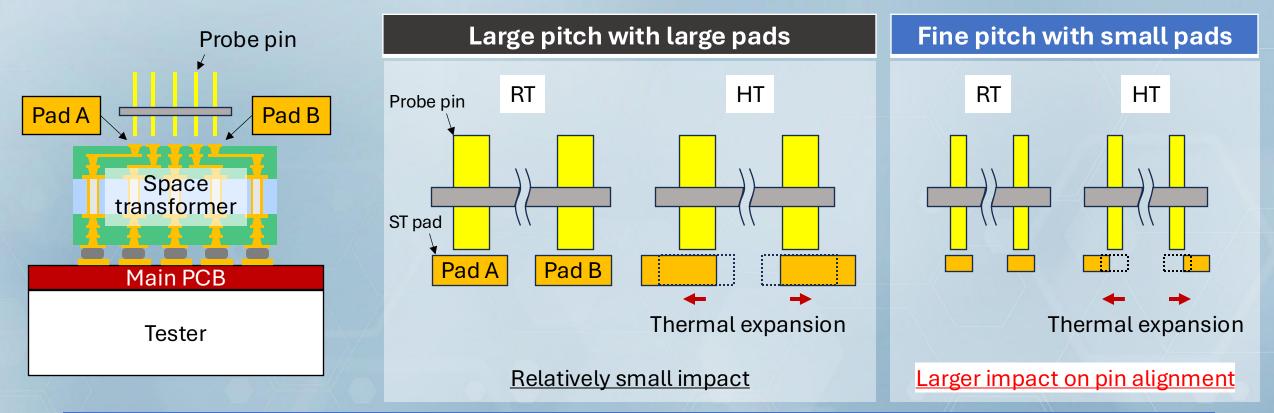

### **Challenge 2 : Pad Position Control by Lowering Substrate CTE**

### Pad position shift by thermal expansion

Influence of thermal expansion becomes larger as DUT pads become smaller. CTE has to be lowered at the same time as fine pitch development.

Yo Nozaka

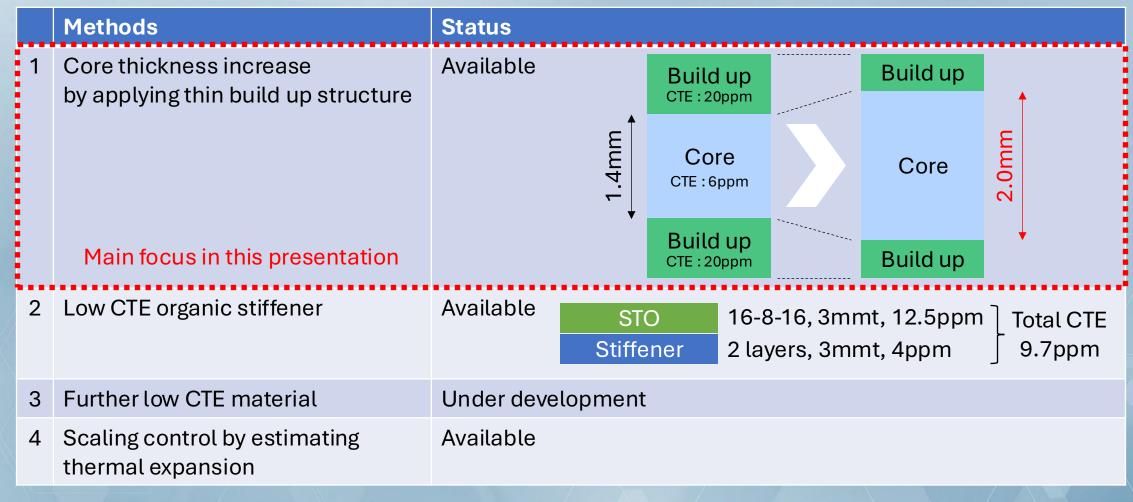

### **Challenge 2 : Pad Position Control by Lowering Substrate CTE**

### Methods for lowering substrate CTE

Yo Nozaka

#### TOPIC 2: Fine Pitch Development

# Test Vehicle Specification (Challenge 2 : Pad Position Control)

|  | Speci                       | SpecificationsConventional build up<br>& Low CTE material |                                   | (New) Thin build up<br>& Low CTE material |

|--|-----------------------------|-----------------------------------------------------------|-----------------------------------|-------------------------------------------|

|  | Substrate size              |                                                           | 72mm*72mm*3mmt<br>(Core : 1.4mmt) | 72mm*72mm*3mmt<br>(Core : 2.0mmt)         |

|  | La                          | ayers                                                     | 16-8-16                           | 16-8-16                                   |

|  | CTE<br>[ppm] Core<br>Copper |                                                           | 6                                 | 6                                         |

|  |                             |                                                           | 20                                | 20                                        |

|  |                             |                                                           | 16.5                              | 16.5                                      |

|  |                             | Core                                                      | 34                                | 34                                        |

|  | Modulus<br>[GPa]            | Build up film                                             | 13                                | 13                                        |

|  |                             | Copper                                                    | 130                               | 130                                       |

|  | Build up f                  | ilm thickness                                             | 30µm                              | 15µm                                      |

|  | Laser via diameter          |                                                           | 40µm -50                          | 0% 20μm                                   |

|  | DUT pad diameter            |                                                           | 60µm                              | 30µm                                      |

|  | DU                          | Tpitch                                                    | 80µm -44                          | 45μm                                      |

|  | /                           | 5 <sup>th</sup> Annual SW/Te                              | st Asia   Fukuoka, Japan, Octob   | ner 24 - 25 2024                          |

Yo Nozaka

**TOPIC 2: Fine Pitch Development**

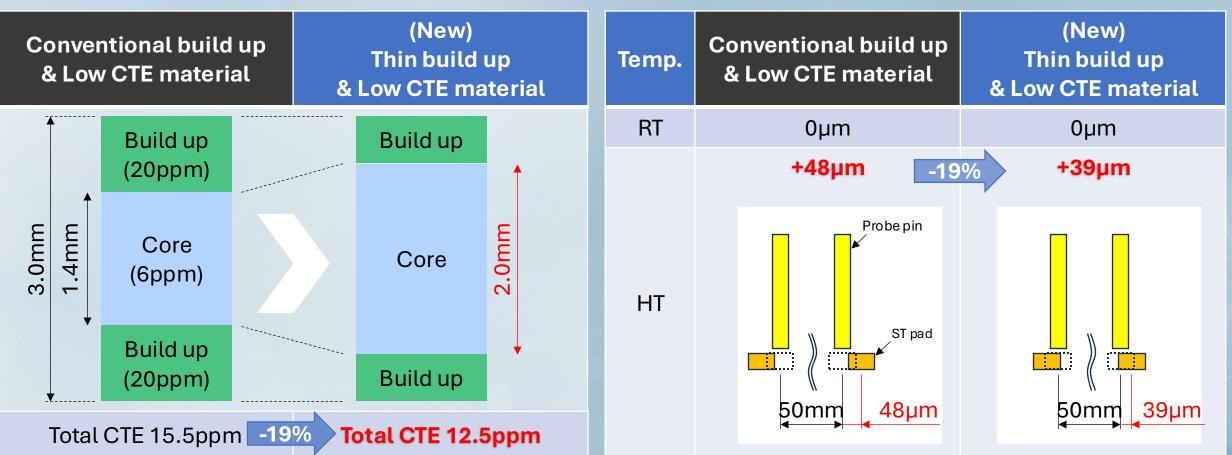

## **Results (Challenge 2 : Pad Position Control)**

#### **Substrate structure and CTE**

#### Thermal expansion (25 to 150deg.C)

### Pad position accuracy was improved by lowering substrate CTE.

Yo Nozaka

# **Future Challenges**

|                      |                | TOPIC 1 : Pin Count Increase                                                                                | TOPIC 2 : Fine Pitch Development                                                                                                                                        |

|----------------------|----------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Goal                 |                | 100K pins by 2024<br>200K pins by 2030                                                                      | 45µm pitch by 2024<br>30µm pitch by 2026                                                                                                                                |

| Challenges           |                | Increasing build up layers<br>up to 20 and more                                                             | <ol> <li>Fine via pitch by using thin build up structure</li> <li>Pad position control by lowering substrate CTE</li> </ol>                                             |

| Results              |                | 100K pins structure with 20 build up layers was realized by controlling CTE mismatch.                       | <ol> <li>45µm pitch structure was developed<br/>by using thin build up structure.</li> <li>Pad position accuracy was improved<br/>by lowering substrate CTE.</li> </ol> |

| Futuro               | Near<br>future | 200K pins structure development by 2030                                                                     | Development of fine pitch of 30µm by 2026<br>⇒ Further thin build up structure                                                                                          |

| Future<br>Challenges | Beyond<br>2030 | Lowering CTE and warpage of substrate<br>with higher build up layers<br>G-ALCS Technology (Glass Substrate) | Development of fine pitch of 20µm<br>⇒ G-ALCS Technology (Glass Substrate)                                                                                              |

| Yo Nozaka            |                | 5 <sup>th</sup> Annual SWTest Asia   Fukuoka, Japan, (                                                      | October 24 - 25, 2024 24                                                                                                                                                |

# G-ALCS Technology (Glass Substrate)

### Glass All-Layer Z-Connection Structure Technology

# What is G-ALCS?

#### Current technology

**F-ALCS**

High layer PCB

F-ALCS core

FICT LIMITED

CHNC

STO with F-ALCS core

Yo Nozaka

New technology

### G-ALCS Class All Layer Z-Connection Structure paste

### Features and benefits of our glass lamination

| Feature               | Benefit                                        |

|-----------------------|------------------------------------------------|

| Stack of thinner TGV  | Yield and lead time imp. for high aspect ratio |

| Resistance to bending | Higher tolerability                            |

| Stack of glass        | Components embedding                           |

| Any layer routing     | Design flexibility                             |

| Low warpage           | Fine pitch routing                             |

#### **Glass Core Space Transformer Organic core Glass core Build up layers** 31 5243244 Ex:4LCore Organic Glass Structure **G-ALCS** core layers Ex: 2LCore CTE 6-16ppm/°C 3-7ppm/°C Modulus 10-40GPa 50-90GPa Tg 150-300°C >600°C Build up layers tanδ 0.003-0.01 0.001 0.1-1.0 < 0.05 Roughness

Yo Nozaka

## **Characteristics of G-ALCS**

Yo Nozaka

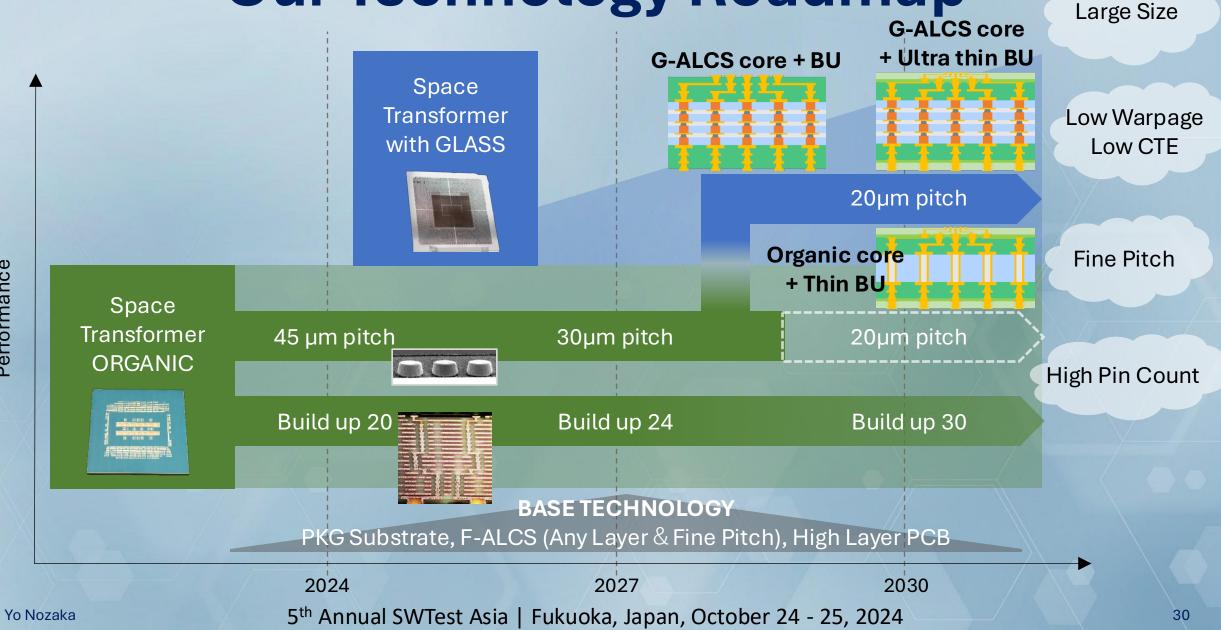

# **Future Challenges with G-ALCS**

|                      |                | TOPIC 1 : Pin Count Increase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TOPIC 2 : Fine Pitch Development                                         |

|----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Goal                 |                | 100K pins by 2024<br>200K pins by 2030                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45μm pitch by 2024<br>30μm pitch by 2026                                 |

| Future<br>Challenges | Beyond<br>2030 | Lowering CTE and warpage of substrate with higher build up layers<br>G-ALCS Technology (Glass Substrate)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Development of fine pitch of 20µm<br>G-ALCS Technology (Glass Substrate) |

| G-ALCS<br>Technology |                | Material properties allowing<br>Low CTE and Warpage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20µm pin pitch by G-ALCS core with ultra thin build up structure         |

|                      |                | <pre>     for the second secon</pre> | G-ALCS core + Ultra thin BU                                              |

# **Our Technology Roadmap**

# Conclusion

### Latest Development Status of Space Transformer Organic

- Achievements

- 100K pins structure with 20 build up layers

- 45µm pin pitch using thin build up structure

- Higher pad position accuracy by lowering substrate CTE

- Future Challenges

- 200K pins structure with build up layers up to 30 by 2030

- 30µm pin pitch using further thin build up structure by 2026

### Breakthrough Technology : G-ALCS (Future challenges beyond 2030)

- Lowering CTE and warpage of substrate with higher build up layers

- 20µm pin pitch by G-ALCS core with ultra thin build up structure

# THANK YOU!

If you have any questions, feel free to visit our Booth (No.307) Or send an e-mail : fict-exhibition@fict-g.com

#### Latest Information Available on:

@fict9961

Yo Nozaka