### Cleaning Innovations to Maximize OEE for High Volume Memory Test

| $\sim$   |

|----------|

| JEM      |

| $\smile$ |

#### Victoria Tran, PhD

R&D Director Gel-Pak

#### **Tomonao Nakashima**

Chief Manager of Product Engineering Japan Electronic Materials Corporation (JEM)

### **Overview**

- Gel-Pak and JEM Corporate Snapshots

- Background and Motivation

- Material Design

- Proof of Concept

- Testing and Results

- Summary / Conclusion

- Next Steps

#### **Innovative Solutions that Drive OEE**

**40-Years of Materials Expertise**

#### Three ISO 9001-2015 Certified Manufacturing Facilities:

- Over 95,000 square feet of Materials Manufacturing

- ISO Class 10,000 Cleanrooms

- **ISO Class 7 Cleanrooms**

- Over 200 Employees •

- Global Sales and Applications Support Network

# **Japan Electronic Materials**

ROPE S.A.R.I

JEM TAIWAN

EM SE ASIA

JEM (THAILAND) CO.,LTD.

M AMERICA CORP.

MCO CO.,LTD

OUTH KOREA

EM SHANGHA

M (HONG KONG

ATE OF CALIFORN

DOUARTER

SANDA FACTORY

PLANT

- Since 1970, JEM has contributed to the growth and development of the global semiconductor industry.

- 4 sites in Japan, 6-sites throughout Asia, 1-site in US, and 1-site in EU

- Key supplier of Advanced MEMs Type Probe cards for Memory and Logic Device Testing

MC Series - MEMS Micro Cantilever Type for Memory Test

- High-parallelism testing and fine-pitch pads

- High density memory, DRAM, NAND, and Flash

-8

#### MT Series - Vertical MEMS Type for Fine-Pitch Area Array

- High-parallelism testing and fine-pitch pads and Cu pillars.

- Area array, Logic Devices, and MPU / AP

### **Overview**

- Gel-Pak and JEM Corporate Snapshots

- Background and Motivation

- Material Design

- Proof of Concept

- Testing and Results

- Summary / Conclusion

- Next Steps

## Mission of Wafer Test | Critical Data

Image Source: Verigy

**Provide Feedback to FAB** for Wafer Manufacturing

**Provide Performance Data to Improve Design**

**Categorize Devices** based on performance

Maintain High Yields during high volume testing

Facilitate High Density Multi-Die with "KGD" Solutions

**Reduce Costs of Yield Loss at Final Test**

Test Provides Metrology For Entire Semiconductor Value Chain

5<sup>th</sup> Annual SWTest Asia | Fukuoka, Japan, October 24 - 25, 2024

Source: SWTest Asia 2019 – Ozawa Keynote

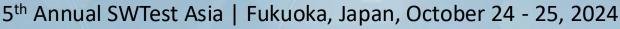

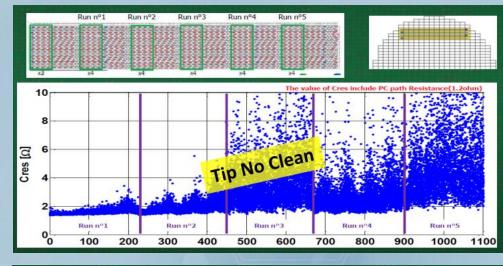

### **Data Quality Attained with Probe Cleaning**

OEE Loss Occurs during Continuous Probing without a Cleaning Process

### **Efficient Probe Cleaning:**

- Improves test accuracy: Removes debris, oxides, residuals, etc., that affect test program performance.

- **Prolongs probe card life**: Consistent cleaning maintains performance and reduces offline repair.

- Reduces risk of contamination: Prevents proberelated debris from dropping onto the wafer and affecting subsequent processing steps.

- Increases prober availability: Assures accurate probe-to-pad-alignment (PTPA) critical for small tips, small device I/Os, fine pitches, and large contactors.

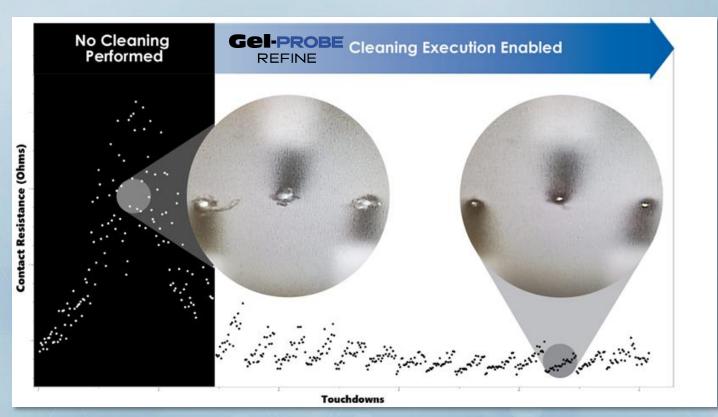

### **Cleaning Challenge | CRES & Lifetime**

- Probes touch the DUT, but the Current Might NOT Flow !

- Probe cleaning is a "dirty business" and critical for controlling contact.

- $\rho_{pad}$ ,  $\rho_{probe}$ ,  $\sigma_{film}$  = resistivity values

- H = hardness of the pads, bumps, pillars, etc.

- P = contact pressure applied by probe

# Implement efficient cleaning to ensure continuously reliable electrical contact.

#### Source: R. Vallauri, D. Perego, M. Prea, J. Kim, and J. Yun, SWTest 2017

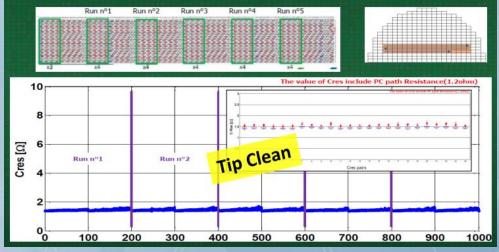

# **Poor Cleaning = High Test Costs !**

- Cleaning can consume more

95% of a probe card lifetime.

- With aggressive cleaning test costs increase.

Aggressive Cleaning Reduces Probe Card Life

Optimal Cleaning Probe Card Life Maximized

3/4/2025

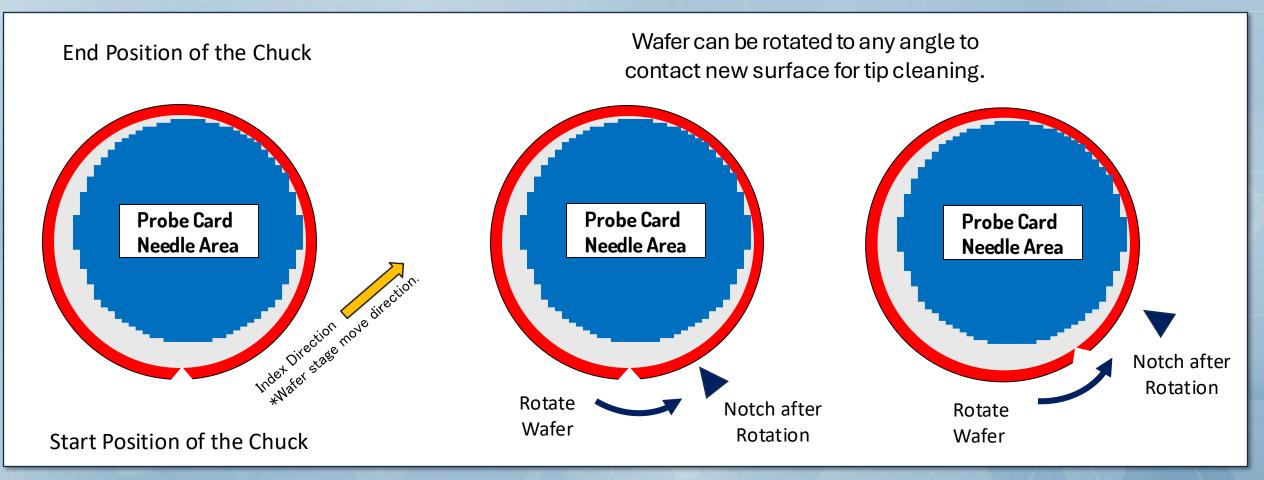

# **High Volume Probers for Improved OEE**

#### **Multi Test-Cell Systems**

- Accommodate large array and full wafer testing.

- Handle multiple probe cards

- Can handle multiple cleaning wafers with execution steps to maintain probe card life-time

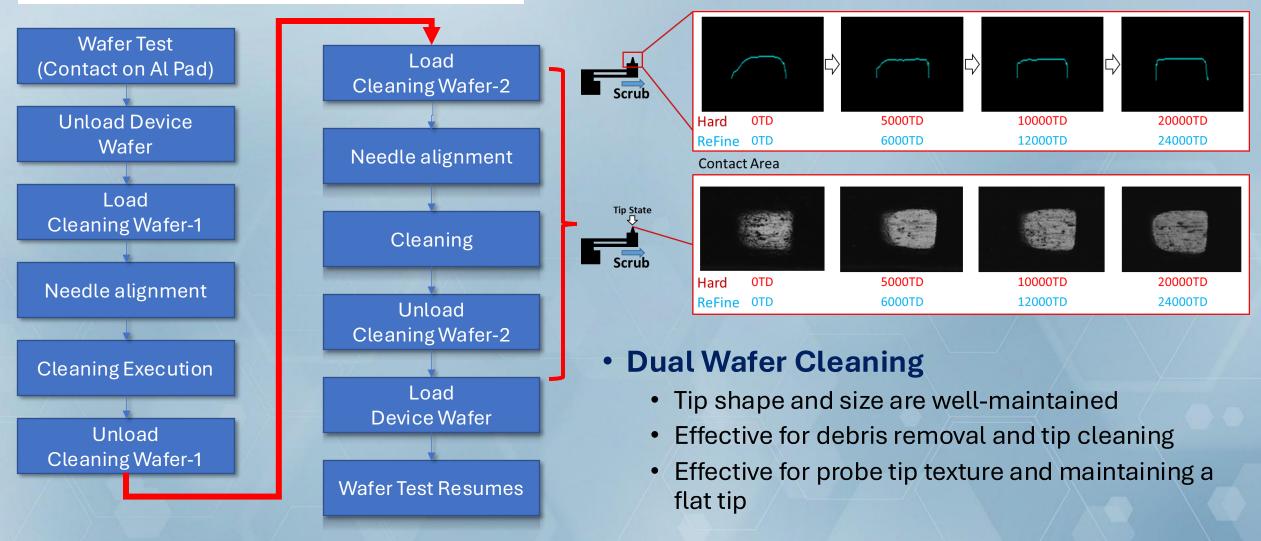

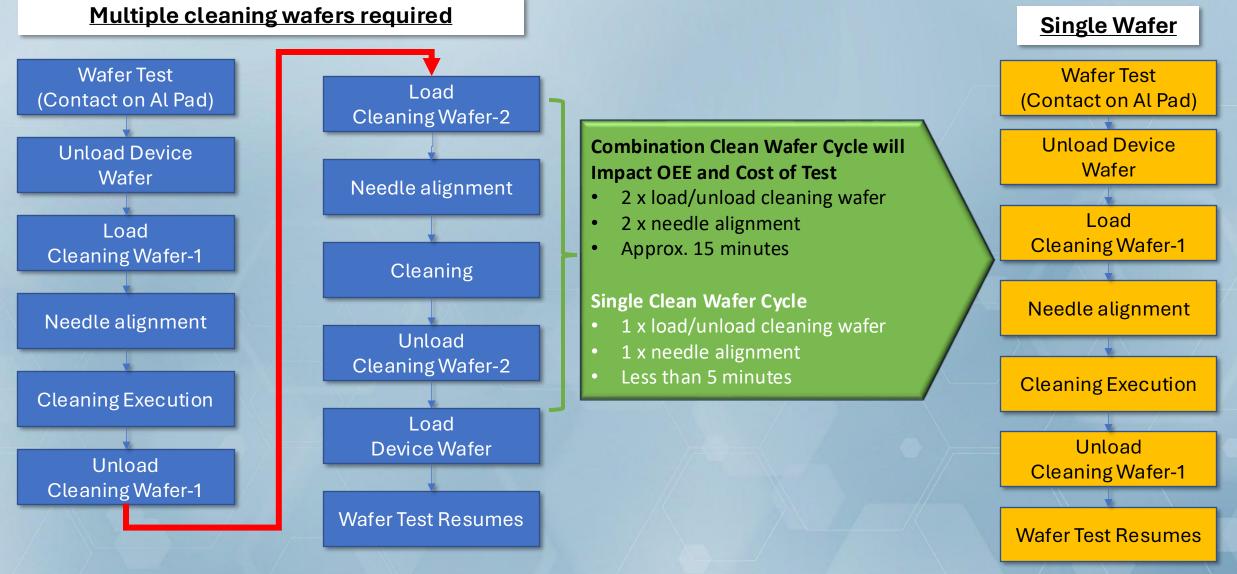

### **Probe Card Cleaning Challenges**

- Probe card technology + cleaning material tracking is critical.

- One material may be fully utilized before the other.

- Loading & unloading multiple cleaning wafers can reduce OEE.

**TEL Cellcia Modular Prober**

#### Minimizing Number of Cleaning Materials Can Improve OEE

5<sup>th</sup> Annual SWTest Asia | Fukuoka, Japan, October 24 - 25, 2024 Sources: Accretech and TEL websites 10

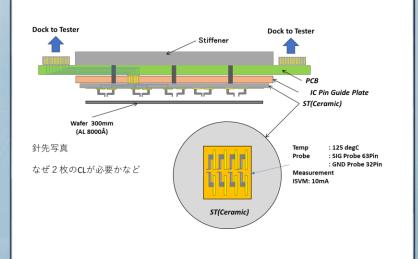

### **One Touch Memory Probe Cards for Improved OEE**

#### JEM MC Series MEMS Micro-Cantilevered

- Fine Pitch and High Pin count

- High Density with MEMS Technology

- High Speed Application

- More Design & Production Capacity

- Mounted onto PCB & Stiffener

#### JEM ML Series MEMS Micro-Cantilevered

- Fine Pitch and High Pin count

- High Density with MEMS Technology

- Specifically designed for Multi Probing System

- Simple structure without PCB and IC-pin

- Lighter weight due to lighter stiffener, easy to handle

Ideal cleaning material must address advanced probe card technologies

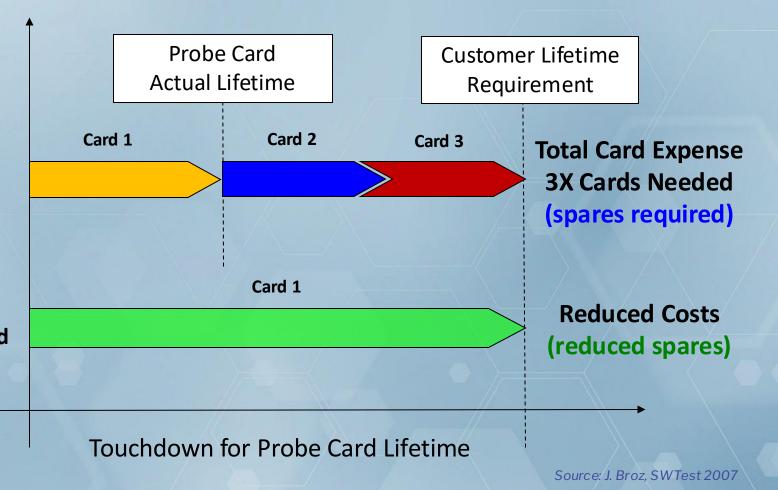

## **Cleaning a Full Wafer Contactor**

- Cleaning wafers stored within the prober are required for single wafer probe card technologies.

- Stepping and indexing during cleaning execution is critical for optimal probe tip maintenance.

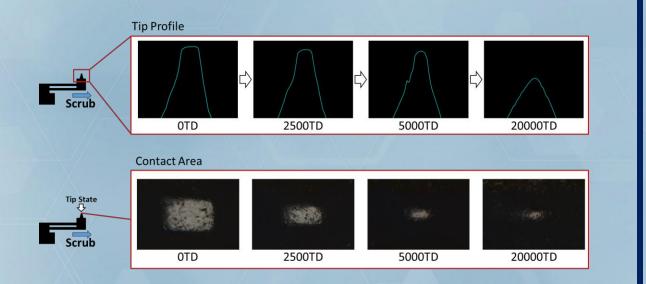

# **Current Cleaning Strategies**

#### Gel-Probe Refine-H3 Cleaning Wafer

- Abrasive loaded elastomer for online cleaning.

- Effective for debris removal and tip cleaning

- Overall, low wear rate for long lifetime

- Difficult to maintain overall probe tip shape

#### Textured silicon cleaning wafer

- Hard cleaning wafer

- Effective for probe tip texture and maintaining a flat tip

- Overall, high wear rate for short lifetime

- Tip size becomes too large.

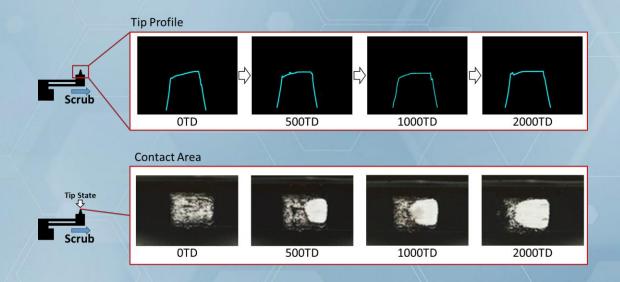

## **Combination Cleaning Process**

#### Multiple cleaning wafers required

# **Optimizing the Cleaning Process**

### **Overview**

- Gel-Pak and JEM Corporate Snapshots

- Background and Motivation

- Material Design

- Proof of Concept

- Testing and Results

- Summary / Conclusion

- Next Steps

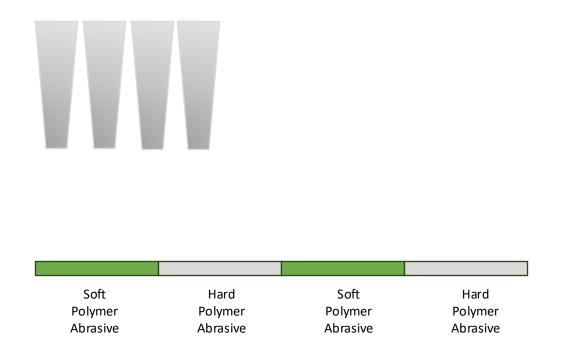

### **Challenge | Multizone Cleaning Material**

#### Goal:

Eliminate the need for a multiplecleaning-wafer strategy for full wafer contact probe cards to improve OEE.

#### **Critical Design Requirements:**

- 1. Zones of hard and soft polymer are planar with a low variability (Rt, peak-to-valley) and TTV.

- 2. Probe-tips will contact both hard and soft abrasive polymer zones during cleaning cycle indexing.

- 3. All zones across the cleaning wafer are thermally stable.

- 4. Zone size, location, and material type are customizable.

Animation demonstrates probe tip cleaning sequence

Patent Pending

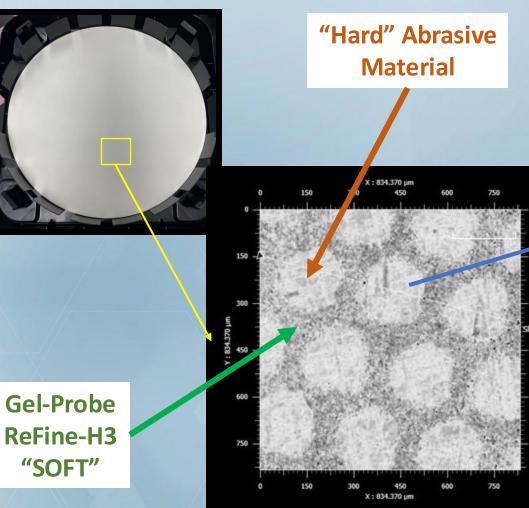

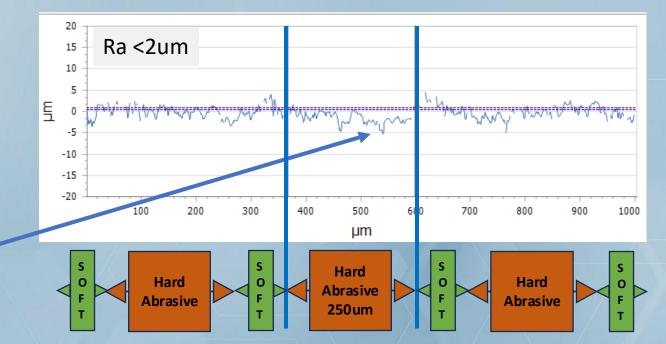

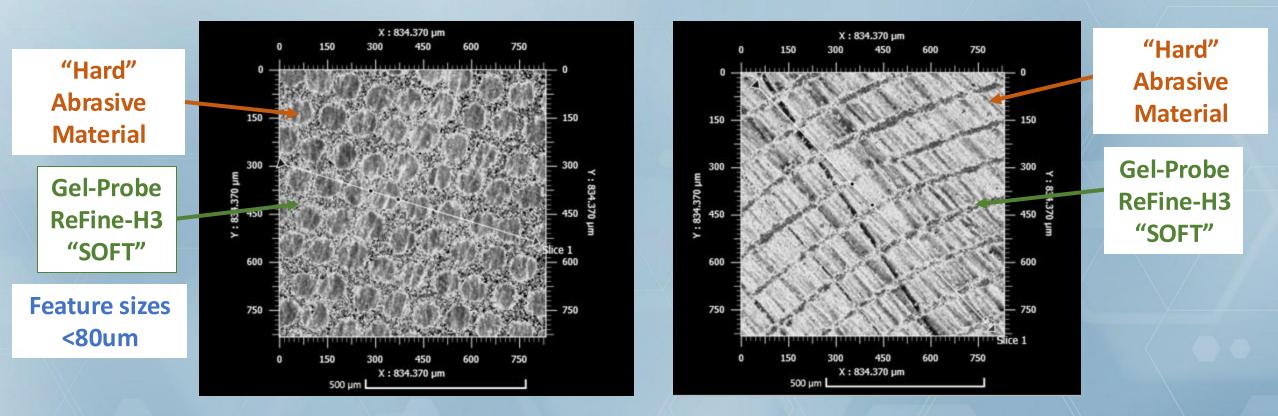

## **Surface Morphology**

300mm Prototype

#### ✓ Design Requirement:

Polymer abrasive and shaping materials are flat and planar at the surface with a low TTV and controlled surface roughness.

Patent Pending

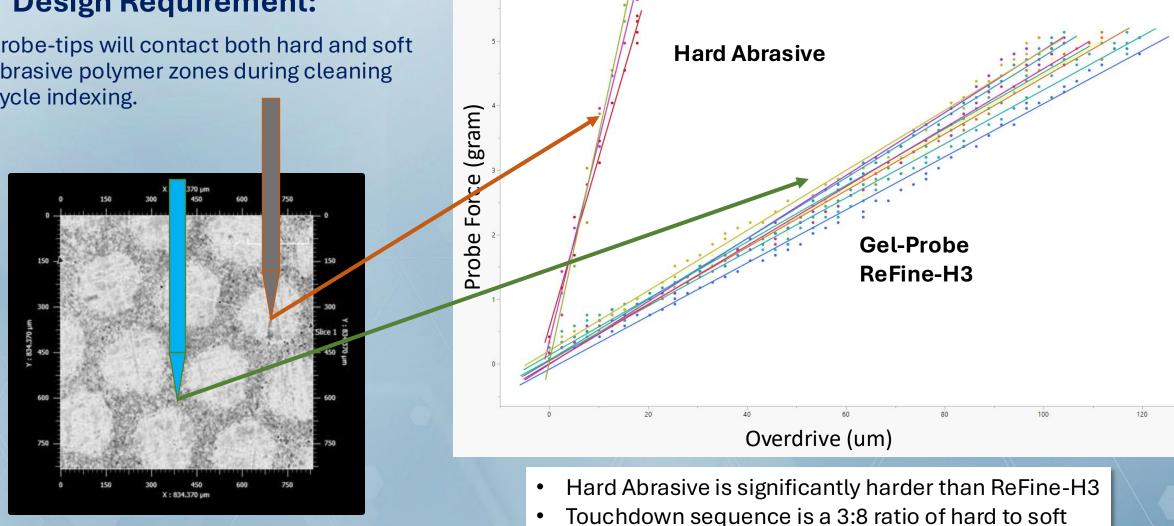

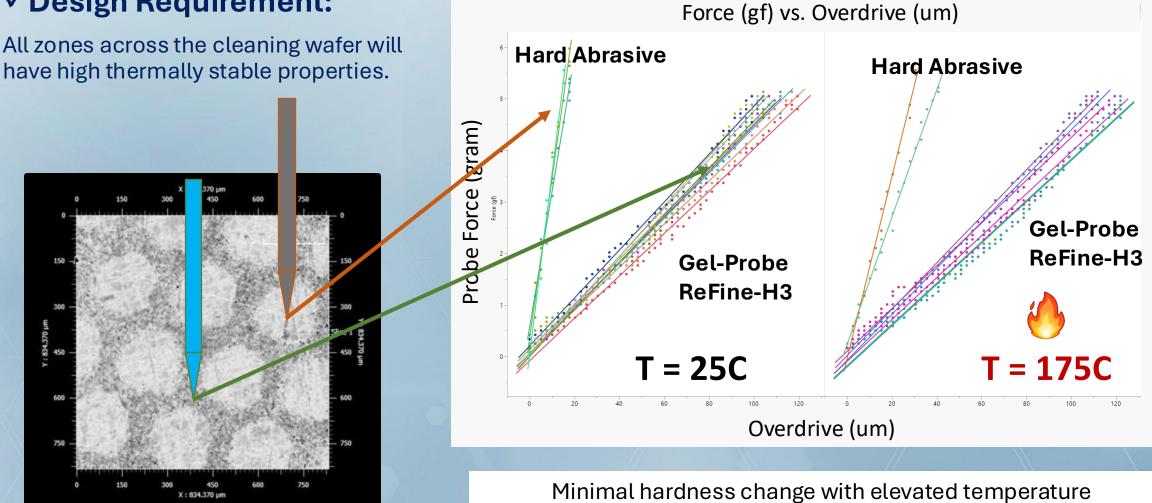

## **Insertion Hardness (Force vs. OT)**

#### ✓ Design Requirement:

Probe-tips will contact both hard and soft abrasive polymer zones during cleaning cycle indexing.

Force (gf) vs. Overdrive (um)

5<sup>th</sup> Annual SWTest Asia | Fukuoka, Japan, October 24 - 25, 2024

Patent Pending

### **Temperature Stability**

#### ✓ Design Requirement:

Patent Pending

### **Customized Surface**

#### ✓ Design Requirement:

Domain size, location, and material type are customizable.

Tunable materials and patterns to match probe card design, prober and cleaning requirements

**Patent Pending**

### **Collaborative Project**

**Cleaning Materials**

300 mm Multi-zone wafer 250 um diameter hard clean domains

VS

Combination Cleaning Gel-Pak GP Refine-H3 (soft cleaning) Silicon Cleaning Wafer (hard cleaning) <u>Test Vehicle</u> JEM MC Probe card for HVM Prober

#### <u>OEE</u> Evaluation

- Debris Removal Efficiency

- CRES Recovery

- Tip Wear Rate

#### Patent Pending

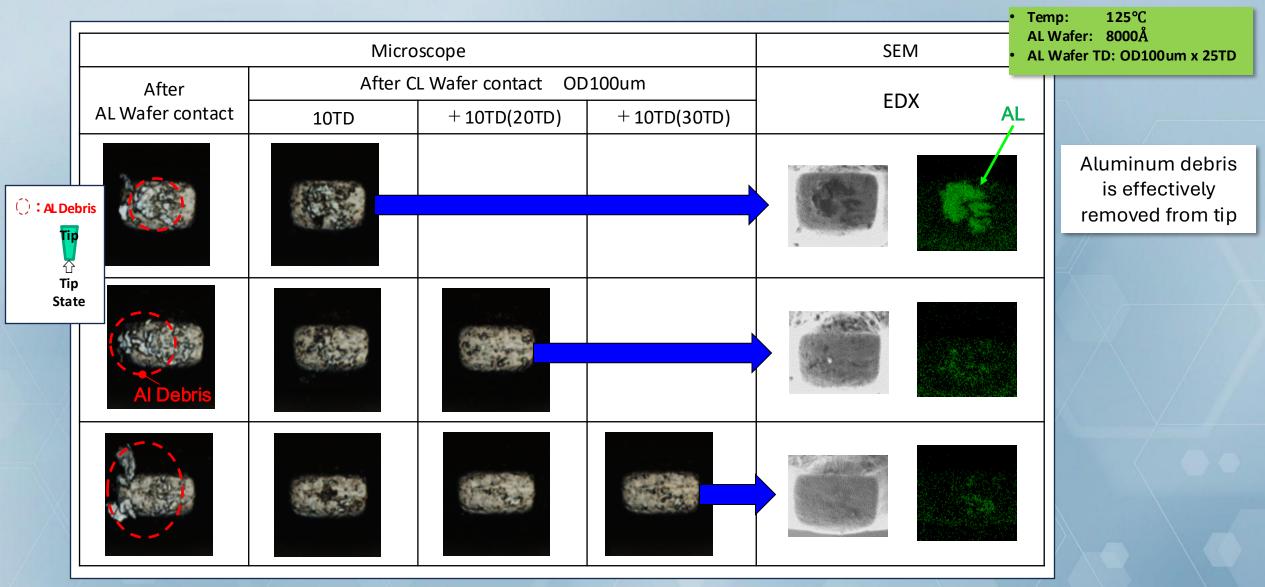

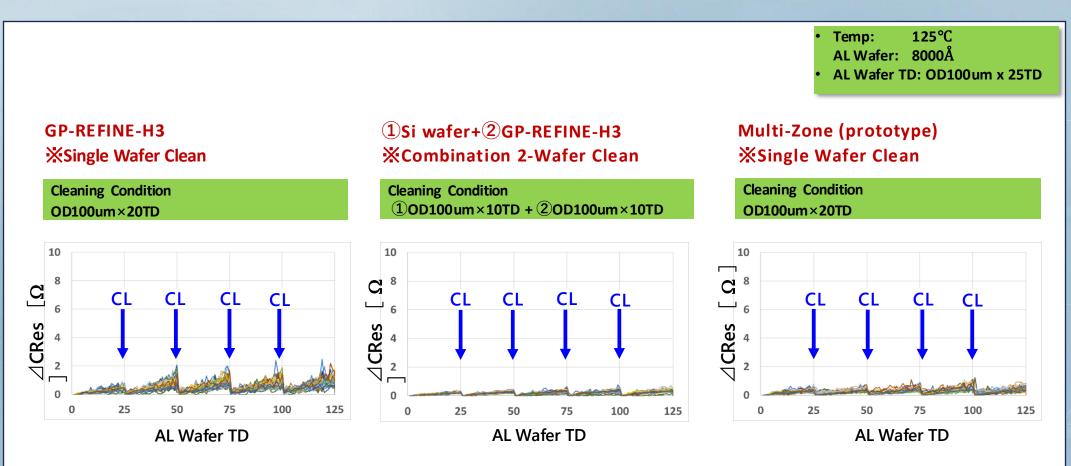

### 1-Wafer Process | Multi-zone Prototype

### 1-Wafer Process | Multi-zone Prototype

CRES recovery of multi-zone prototype is comparable to combination 2-wafer cleaning.

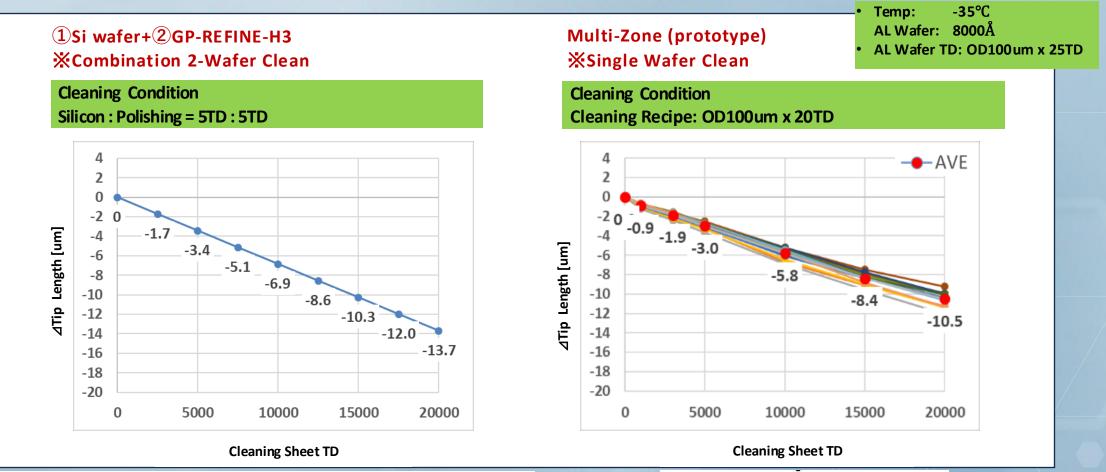

### Low Temp Wear Assessment (T= -35C)

Tip wear of multi-zone prototype is comparable to combination 2-wafer cleaning.

|       | Clear | ning She | et TD |         |

|-------|-------|----------|-------|---------|

| INT   | 6000  | 9000     | 15000 | 20000   |

| Scrub |       | -        | 1990  | -       |

|       |       | N.S.     |       | and the |

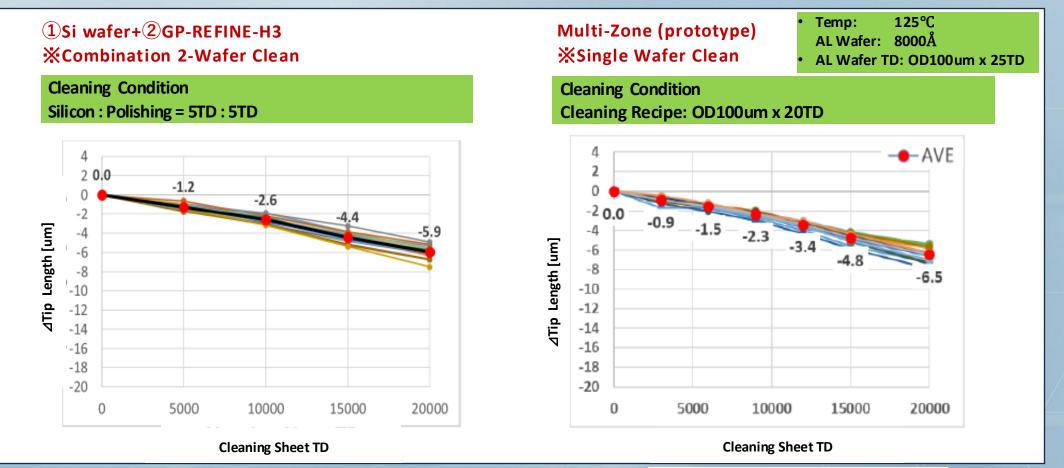

### High Temp Wear Assessment (T= 125C)

Tip wear of multi-zone prototype is comparable to combination 2-wafer cleaning.

| Cleaning Sheet TD |      |      |       |       |  |

|-------------------|------|------|-------|-------|--|

| INT               | 6000 | 9000 | 15000 | 20000 |  |

| Serut Serut       | 0    |      |       | 0     |  |

# Summary | Improved OEE

#### Innovative, Multi-zone, single two step cleaning wafer developed

- Overall cleaning performance result is comparable to combination cleaning conditions.

- High temp and low temp wear rates are equivalent to combination cleaning

- Design and materials are customizable to develop specialized cleaning.

- Simplifies the overall process flow for cleaning single wafer contactors.

#### Eliminates time-consuming, 2-wafer cleaning process for improved OEE.

| OEE Impact<br>(Overall Equipment Effectiveness)<br>Availability x Performance x Quality | Productivity Loss in<br>Manufacturing | 1-Wafer Cleaning Process<br>vs.<br>2-Wafer Cleaning Process |

|-----------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------|

| Availability Loss                                                                       | Downtime                              | Minimize                                                    |

| Availability Loss                                                                       | Wafer Exchanges                       | Minimize                                                    |

| Performance Loss                                                                        | Minor Stops                           | Fewer                                                       |

|                                                                                         | Reduced Speed                         | Fewer                                                       |

| Quality Loss                                                                            | Yield                                 | Maximize                                                    |

| Quality Loss                                                                            | CRES Stability                        | Maximize                                                    |

### **Next Steps**

- Low volume manufacturing

- Customer collaboration and qualification

### Acknowledgements

- Yuki Nakamura

- Masaoki Oyama

- Shohei Sawamura

- Patrick Mui

- Rembrant Gamboa

- Jerry Broz, PhD