## TestGeni - An Intelligent Automation Tool for ATE Engineers

Nachiappan Vaishnavi Caliber Interconnects Pvt Ltd

Hsinchu, Taiwan, October 26-28, 2022

#### **Table of Contents**

| 01 | INTRODUCTION                 |

|----|------------------------------|

| 02 | PROGRAM FLOW IN TESTING      |

| 03 | WHY TESTGENI?                |

| 04 | PROTOTYPE                    |

| 05 | GLIMPSE OF TESTGENI FEATURES |

| 06 | ON TARGET                    |

| 07 | CONCLUSION                   |

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

#### Introduction

Time is money in semiconductor industry

One of the biggest challenges of post silicon validation is time reduction in program development and testing

Automation: An intelligent solution reducing the manual efforts

Caliber intends to provide the best possible automation in test program generation even in the absence of tester tool

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

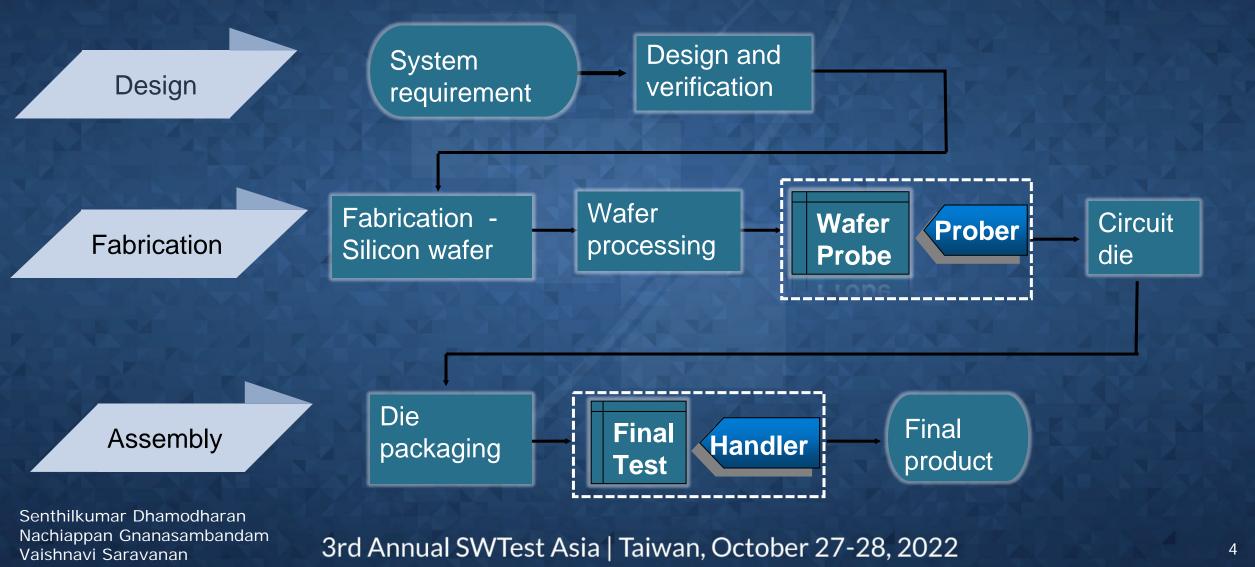

# Post silicon validation in IC manufacture cycle

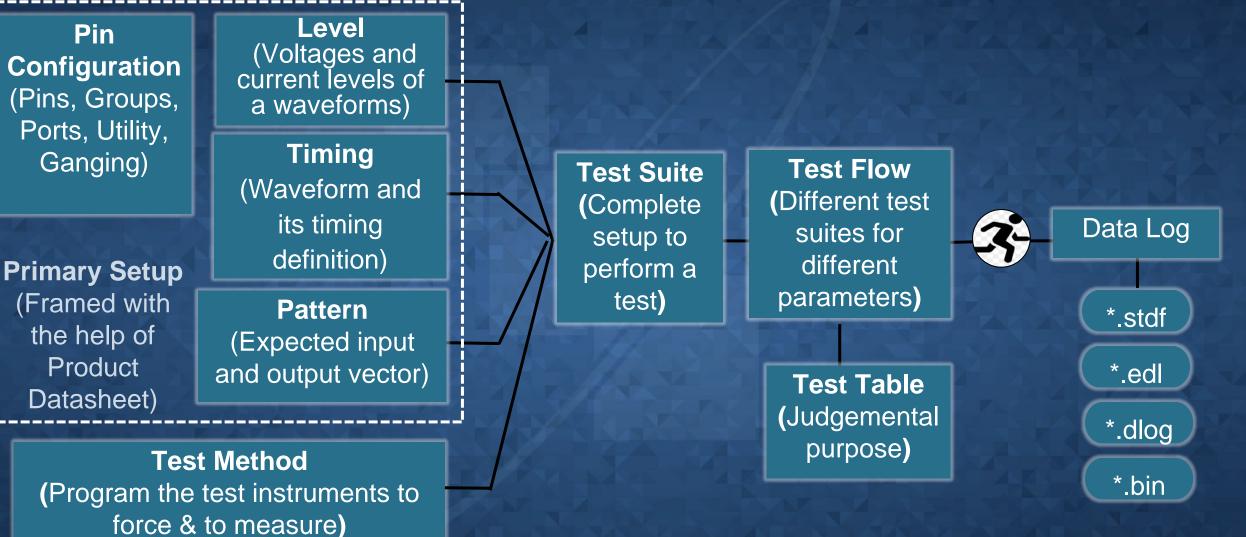

#### **Basic program development flow**

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

#### Why TestGeni?

Quick generation of primary setup files

Huge vector generation, i.e., fault detecting algorithms for memory chip testing

Legacy tester pattern conversion to desired tester platform conversion

Cross portability in production, characterization and debug test flow

Analysis of data log and generation of user defined(Textual & Visual) formats

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

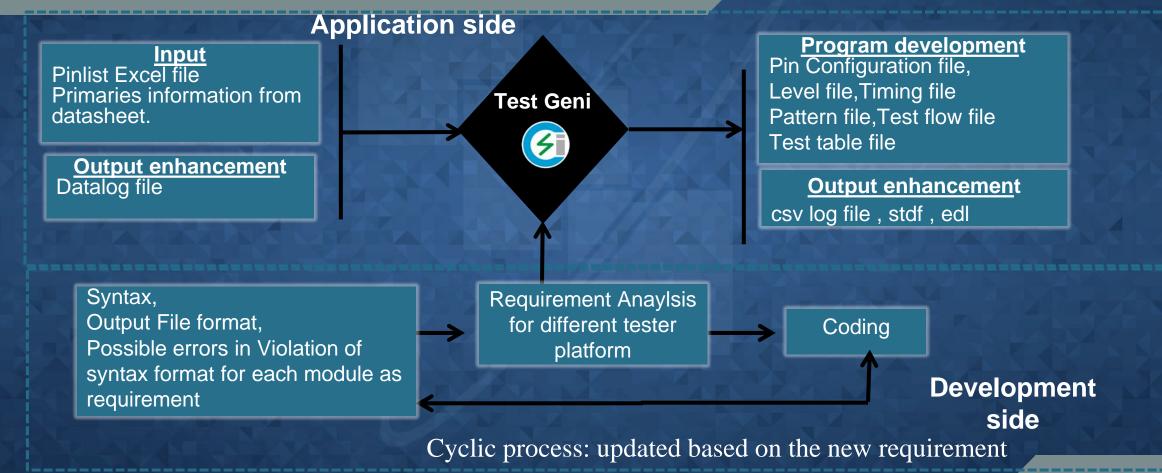

# Prototype model of TestGeni

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

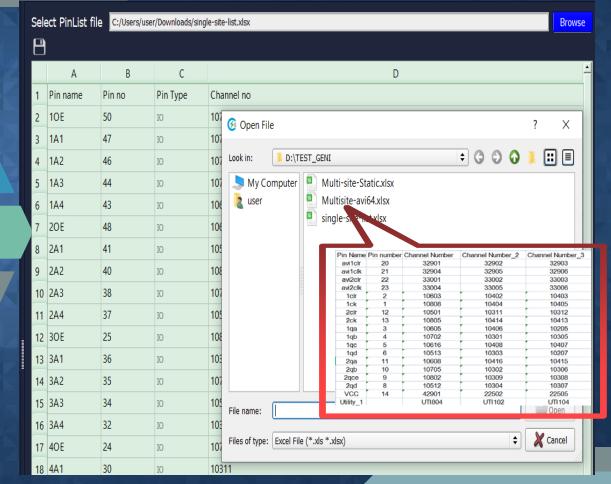

## Automation: Primaries development

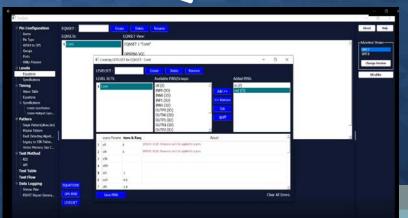

Converts excel file into a loadable pin config file supported by tester tool

Time reduction in feeding pins for primary setup file

Customizable with any kind of pin-info to tester compatible pin config

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

## Automation: Primaries development

User friendly GUI interface in generating primaries and avoids the manual syntax errors

Reduces time in test program development

Supports multiple tester platform

VIL [V] VIH [V] VOL [V] VOH [V] IOL [MA] IOH [MA] DPSPINS VCC vout= VCC vout\_frc\_rng=7 iout\_clamp\_rng=500 ilimit=500 t\_ms=4 offcurr=act #connect\_state= UNGANG LEVELSET1 "LEVSET1\_CONT" PINS cont\_pins vil=VIL

vil=VIL vih=VIH vol=VOL voh=VOH vt=VT iol=IOL ioh=IOH

7 EOUNSET CONT DESSHOR

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

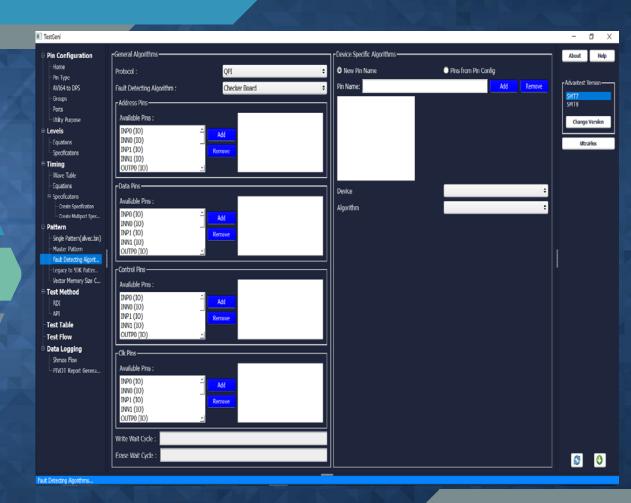

# **Oracle Vector generation**

Easy generation of huge vectors with the help of algorithms.

Incorporation of protocol based predefined fault coverage algorithms.

Vector generation for NOR, NAND Flash memory device specific algorithms

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

#### Expeditious pattern conversion

#### Legacy tester pattern to desired tester pattern conversion

Sample conversion from a legacy tester platform to V93000-SM7 patterns

#### Swift conversion in a single click

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

## Vector memory size calculator

Firmware commands are essential to find the size of vector memory.

TestGeni facilitates user friendly GUI interface with vector and configuration file

Selected pin, port, vector wise memory size calculation

| Pin Configuration                                                         | Select PMF File : ishnavi/IP/LinkedIn_Co  | ntent/Input/vectors/NANDFLASH_W25N01GV2   | ZEIG_DUMMY.pmf Browse PMF File About | Help   |

|---------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------|--------|

| - Home                                                                    | Select CFG file : D:/vaishnavi/IP/LinkedI | n Content/Input/configuration/NANDFLASH W | 25N01GVZEIG.cfg Browse CFG Fie       |        |

| - Pin Type<br>- AVI64 to DPS                                              | FILE NAMES :                              |                                           | CAdvantest Vers                      | sion — |

| - Groups                                                                  |                                           |                                           | SMT7                                 |        |

| - Ports                                                                   | 1                                         | 2                                         | - SMT8                               |        |

| Utility Purpose                                                           |                                           | dIn_Content/Input/vectors/NAND_FULL/CONT  | Change Ver                           | rsion  |

| 🖶 Levels                                                                  | 2 CONTI_FU D:/vaishnavi/IP/Linke          | dIn_Content/Input/vectors/NAND_FULL/CONT  | I/CONTI_FUNC_RECENT                  |        |

| Equations                                                                 | 3 CONTI_FU D:/vaishnavi/IP/Linke          | dIn_Content/Input/vectors/NAND_FULL/CONT  | T/CONTI_FUNC_ZIGZAG_REC Ultrafle     | ж.     |

| Specifications                                                            | 4 FUNC_BL D:/vaishnavi/IP/Linke           | dIn_Content/Input/vectors/NAND_FULL/DC/F  | UNC_BLOCK_ERASE_ML                   |        |

| Timing                                                                    | 5 DC_STAN D:/vaishnavi/IP/Linke           | dIn_Content/Input/vectors/NAND_FULL/DC/D  | C_STANDBY_RECENT                     |        |

| – Wave Table<br>– Equations                                               | PORT NAMES :                              | PIN NAMES :                               |                                      |        |

| Specifications                                                            | SUPPLY_PIN                                | CS                                        |                                      |        |

| Create Specification                                                      | DIGITAL_PINS                              | DO                                        |                                      |        |

| Create Multiport Spec                                                     | CONTI                                     | WP                                        | 1                                    |        |

| Pattern                                                                   |                                           | DI                                        |                                      |        |

| -Single Pattern(alvec.bin)                                                |                                           | HOLD                                      |                                      |        |

| -Master Pattern                                                           |                                           | VCC                                       |                                      |        |

| <ul> <li>Fault Detecting Algorit</li> <li>Legacy to 93K Patter</li> </ul> |                                           |                                           |                                      |        |

| -Vector Memory Size C                                                     | Calculated PORT                           | memory Calculated Pl                      | N memory                             |        |

| Test Method                                                               | PORT memory PORT's no                     | ot found PIN memory                       | PIN's not found                      |        |

| - RDI                                                                     | 1 2                                       | 1 2                                       | L VCC                                |        |

| - API                                                                     | 1 SUPPLY_PIN 18960                        | 1 DO 15432                                |                                      |        |

| Test Table                                                                | 2 CONTI 18960                             | 2 CLK 10016                               |                                      |        |

| -Test Flow                                                                |                                           |                                           |                                      |        |

| 🗄 Data Logging                                                            | 3 DIGITAL 25392                           | 3 DI 12336                                |                                      |        |

|                                                                           |                                           | 4 WP 12768                                |                                      |        |

| Shmoo Flow<br>PIVOT Report Genera                                         |                                           | 5 CS 16520                                |                                      |        |

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

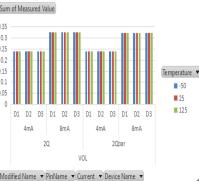

# **Datalogging**

Converting stdf file into an expansive csv file with easily accessible and organised parametrics

Data and test time crunching for quick reporting

Shmoo plot generation from datalog file

|                         | 115.8          | 3 - F        | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|-------------------------|----------------|--------------|--------|-------|----------------------------|--------|---------------|-------|-------------|-----|----------|--------|-------------|------|-----|-----|-----|---|-----|

|                         | 115.88         | 3 - F        | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|                         | 115.96         | 5 - F        | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|                         | 116.04         | 1 - F        | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

| _                       | _ 116.12       | 2 - F        | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

| 1H <sup>2</sup>         | 116.2          | 2 - F        | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|                         | 116.28         | 3 - F        | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   | _   |

| i ti                    | 5 116.36       | 5 <u>-</u> F | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   | F F |

| TIM 2 f@Dinital[MHz     | 116.44         | _            | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

| 5 f                     | 116.52         | _            | Р      | Р     | Р                          | Р      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

| IN                      | 116.6          | _            | Р      | Р     | Р                          | Р      | Р             | P     | Р           | Р   | Р        | Р      | Р           | Р    | Ρ   | Р   | Р   |   |     |

| ľ                       | 116.68         | _            | Р      | F     | Р                          | F      | Р             | Р     | Р           | Р   | Р        | Ρ      | Р           | Р    | Р   | Р   | Р   |   |     |

|                         | 116.76         | _            | F      | F     | F                          | F      | Р             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|                         | 116.84         |              | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|                         | 116.92         | -            | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|                         | 117.0          | D <u>F</u>   | F      | F     | F                          | F      | F             | F     | F           | F   | F        | F      | F           | F    | F   | F   | F   |   |     |

|                         |                | 0.0          | 0.4    | 0.8   | 1.2                        | 1.6    | 2.0           | - 2.4 | 5.2<br>8.2  | 3.2 | 9.0<br>N | 4.0    | 4.4         | 4.8  | 5.2 | 5.6 | 6.0 |   |     |

|                         | A              | В            |        | С     |                            | D      | E             |       | F           | G   |          | н      | 1           | J    | K   | L   | М   | N | 0   |

| 1 Sum of Measured Value |                |              |        |       |                            |        | Temperature 💌 |       |             |     |          |        |             |      |     |     |     |   |     |

| 2                       | Modified Nar 🔻 | PinName      | ▼ Curr | ent [ | <ul> <li>Device</li> </ul> | Name 💌 |               | -50   | 25          |     | 125      |        |             |      |     |     |     |   |     |

| -                       | VOL            | 2Q           | 4mA    |       | D1                         |        |               |       | 0.240723997 |     |          | Sum of | Measured Va | alue |     |     |     |   |     |

| 4                       |                |              |        |       | D2                         |        |               |       | 0.240437999 |     |          | 0.35   |             |      |     |     |     |   |     |

2

Modified Name

PinName

Current

Device Name

-50

25

12

3

VOL

2Q

4mA

D1

0.240437999

0.240439995

0.240439995

0.240439995

0.240439995

0.240439995

0.240439995

0.240324005

0.35

0.35

0.35

0.35

0.35

0.35

0.35

0.37

0.240324005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

0.324503005

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

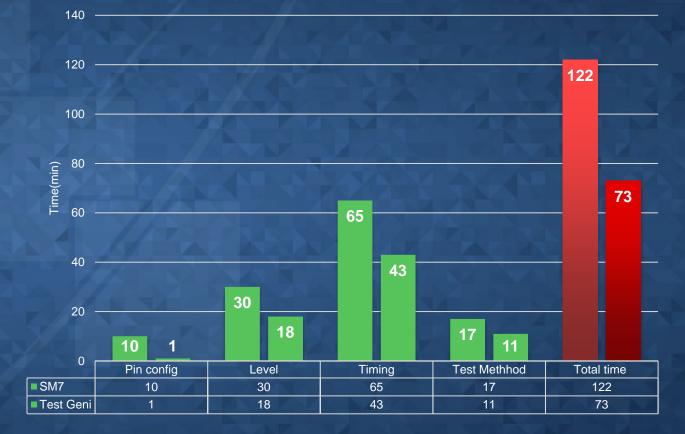

#### **On Target**

#### Use case

- ✓ Real time product: Digital ASIC

- Tester platform: Advantest 93k

Version : SM7

- Test program development is implemented in both tester tool and TestGeni.

- Approximately 41.6% of time is saved using TestGeni

#### **Development Time**

SM7 Test Geni

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

#### **Conclusion and future work**

- TestGeni helps in possible automation needed for test program development and analyses the test data which reduces the man hours

- Incorporating new tester platforms for portability and other advanced features is in progress to reduce the development time further

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan

Senthilkumar Dhamodharan Nachiappan Gnanasambandam Vaishnavi Saravanan