### **Challenges and Improvement Actions for HPC Wafer Testing**

Oscar Lee

HI Tsai

TSMC

Hsinchu, Taiwan, October 26-28, 2022

### Overview

- Introduction

- HPC Challenges

- High Force

- High Power

- High Temperature

- Summary

### **HPC Demand**

The demand of HPC (High Performance Computing) growth rapidly.

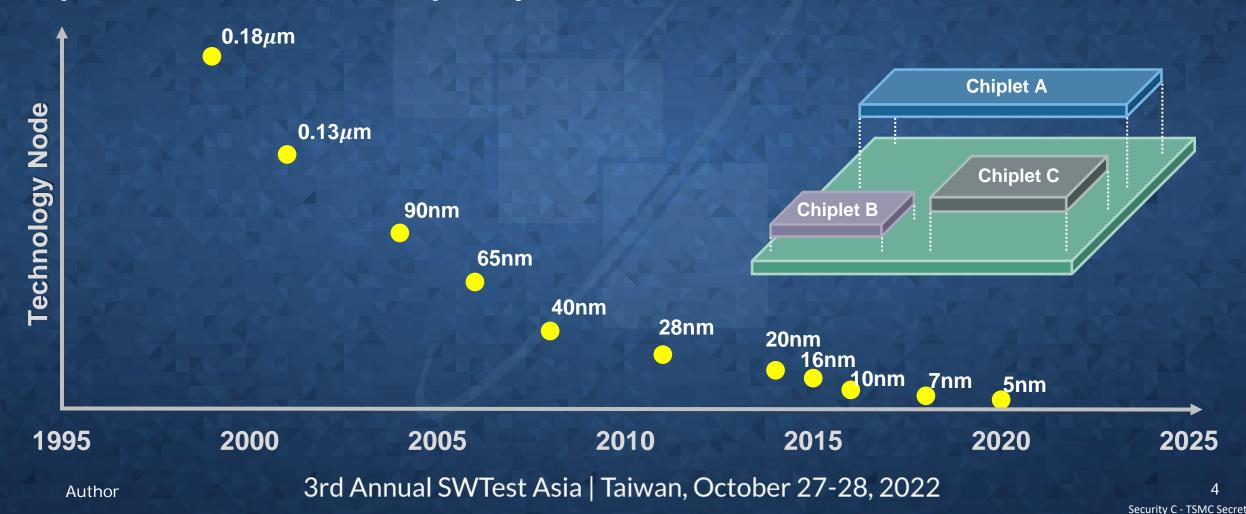

### **HPC Testing Challenges**

With the development of technology node and advanced integration process, the device complexity increase.

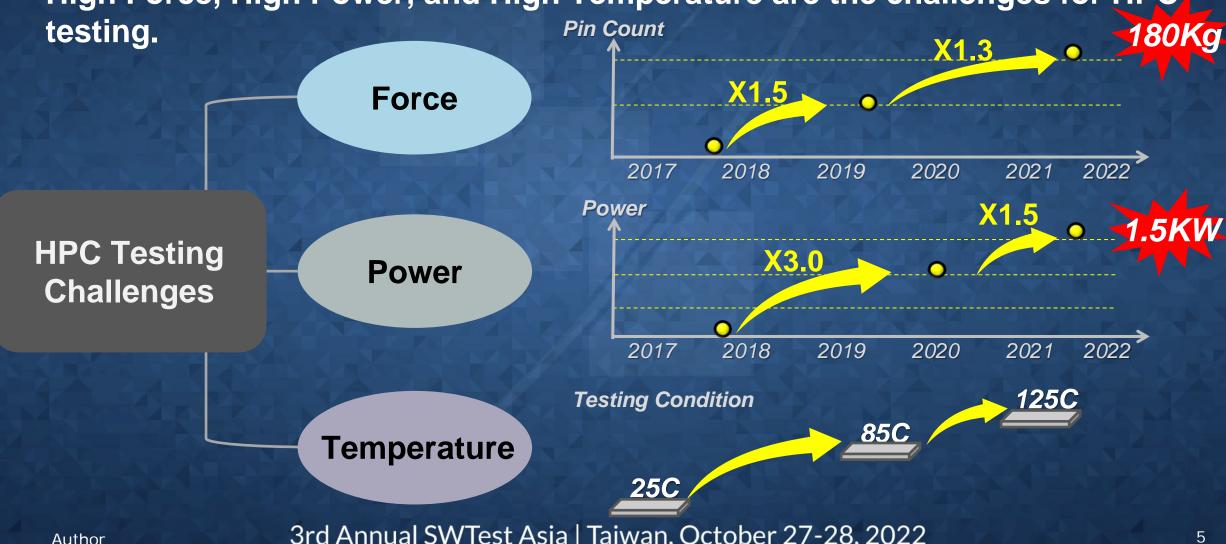

## **HPC Testing Challenges**

High Force, High Power, and High Temperature are the challenges for HPC

3rd Annual SWTest Asia | Taiwan, October 27-28, 2022

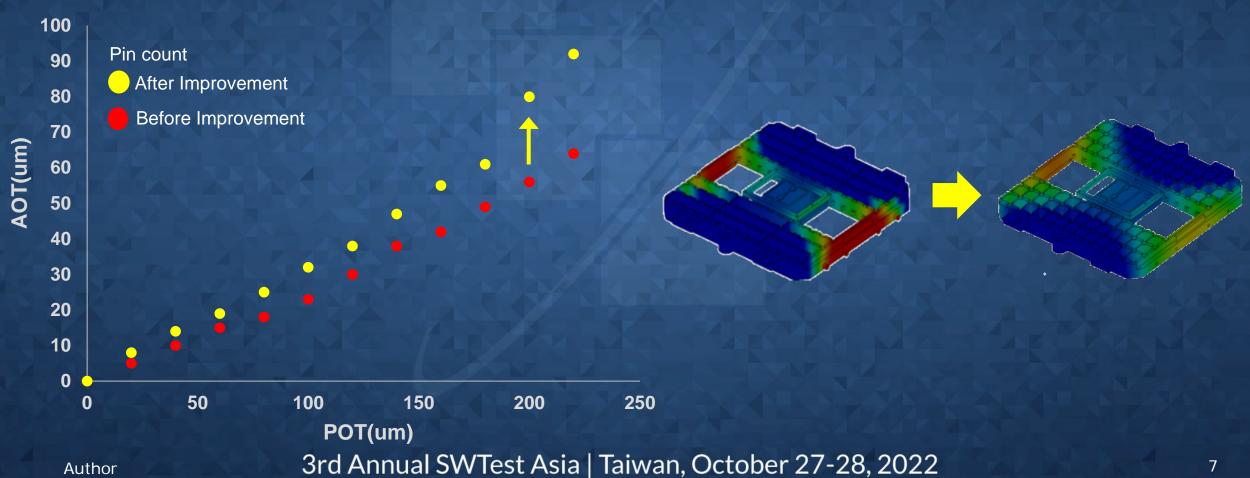

- Observation

- For high pin count probe card, AOT decrease obviously caused by PCB deformation.

**Improvement Action**

Author

► Improve AOT 43% by (1) Stiffener Structure Enhancement (2) Material Enhancement.

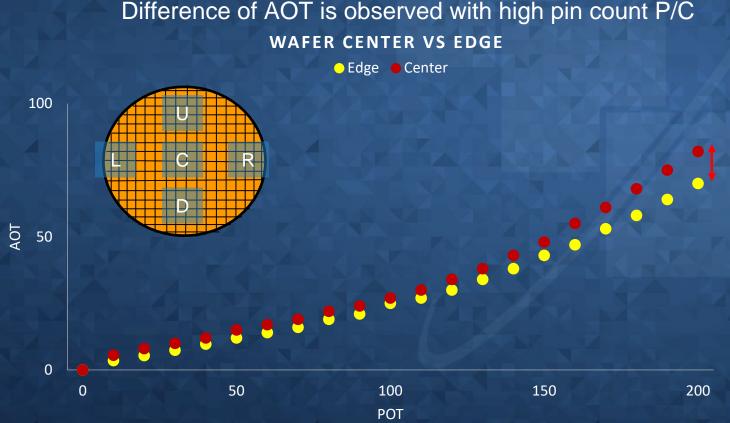

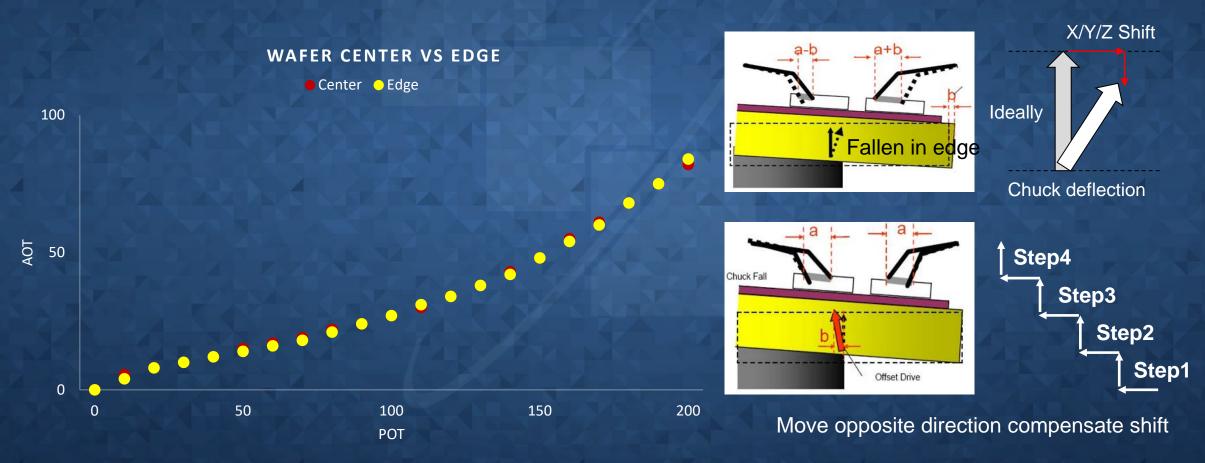

- Observation

- The non-uniform AOT is observed with high pin count testing.

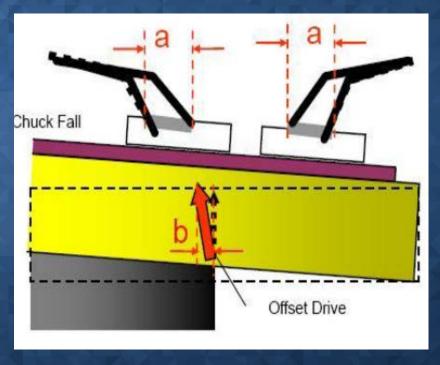

#### Chuck Deflection issue

- Improvement Action

- Enable chuck offset function to compensate chuck bending issue.

3rd Annual SWTest Asia | Taiwan, October 27-28, 2022

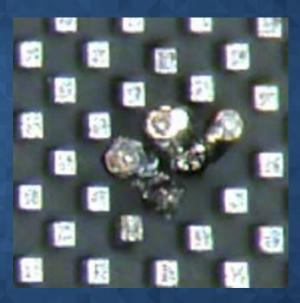

- Observation

- The higher tip burnt rate is observed in HPC testing.

- Improvement Action

- Hybrid probing: The probe with higher CCC is used in pitch > 100um.

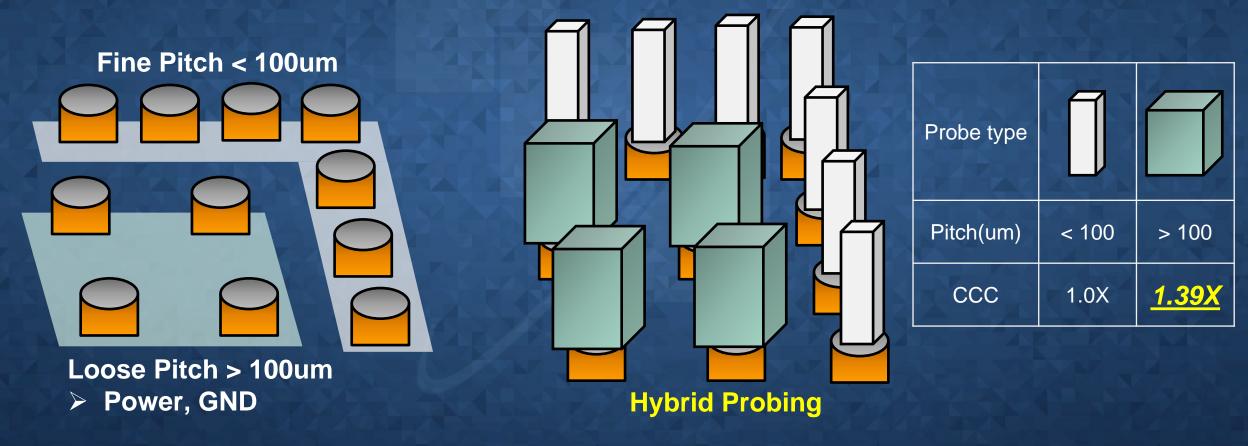

#### Observation :

Temperature accuracy and heat dissipation will be challenges under high power testing.

- Improvement Action

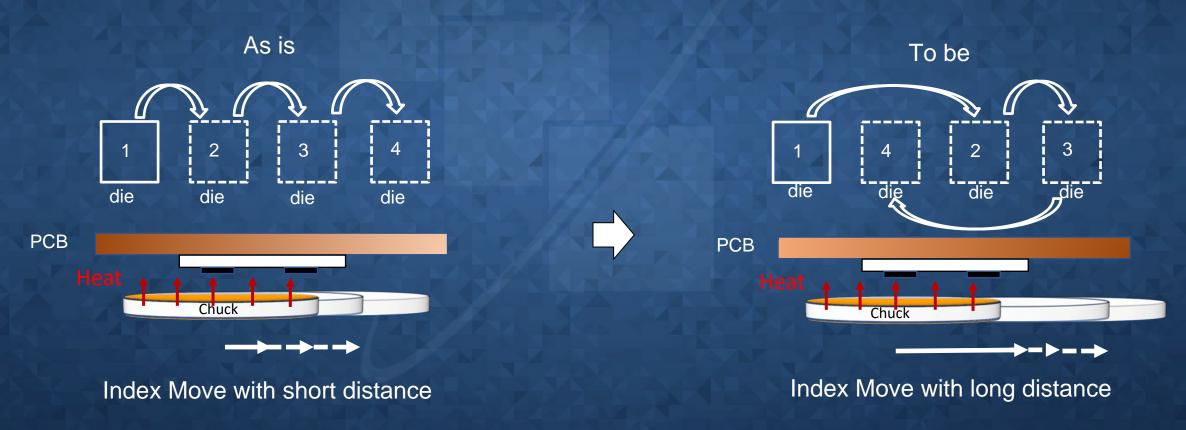

- 1) Index move optimization: Index move is changed from short distance to long distance to improve PCB temperature uniformity.

- Improvement Action

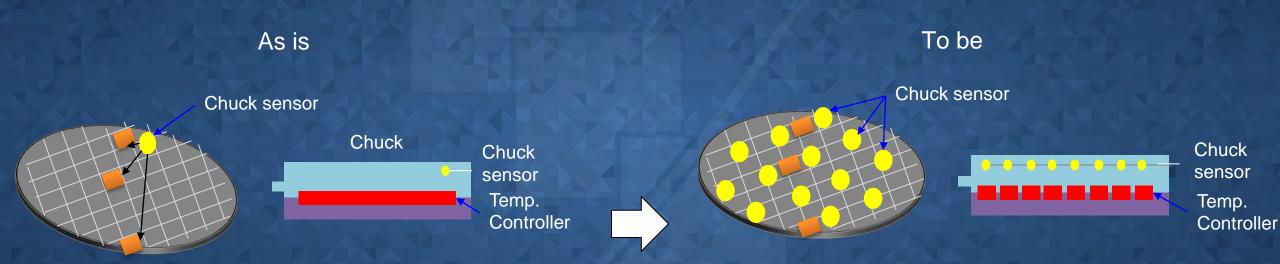

- 2) Control temperature actively by multiple sensor and control zones.

One sensor chuck Temp. control from 1 point temp.

Multi sensor chuck

Temp. control with individual area

- Observation

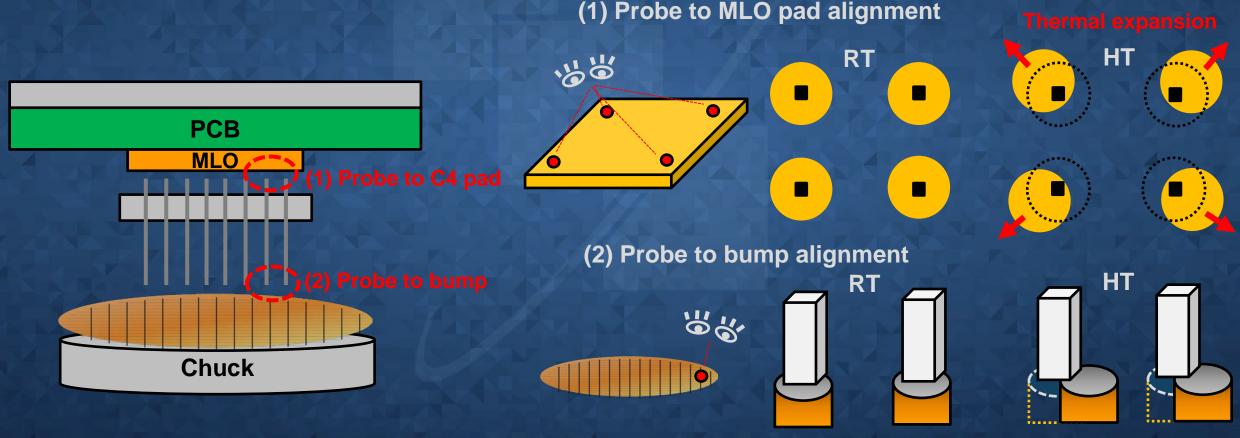

- Due to CTE(Coefficient of Thermal Expansion) difference, the alignment of (1) <u>Probe to MLO pad</u> (2) <u>Probe to bump</u> will shift at high temperature testing condition.

- Improvement Action

- > To improve the alignment, we can optimize below factors.

| Parts         | Key Factors           | Controllable |

|---------------|-----------------------|--------------|

| MLO           | Pad size              | 0            |

|               | Manufacture Tolerance | 0            |

|               | CTE                   | X            |

| Probe Head    | Scaling               | 0            |

|               | CTE                   | X            |

| Wafer         | Probing Area          | 0            |

|               | Pitch                 | X            |

|               | CTE                   | X            |

|               | Testing temperature   | X            |

|               | Bump size             | X            |

| Prober/ Chuck | CTE                   | X            |

|               | Alignment Technology  | 0            |

- Improvement Action for (1) <u>Probe to MLO pad</u> alignment

- 1) Control the scaling of MLO dimension toward negative tolerance.

- 2) Enlarge MLO Pad size to avoid contact issue.

- 3) Design scaled UD to compensate MLO thermal expansion.

3rd Annual SWTest Asia | Taiwan, October 27-28, 2022

- Improvement Action for (2) <u>Probe to bump</u> alignment

- 1) Constrain probing area.

- 2) Design scaled LD to compensate wafer thermal expansion.

**Constrain probing area**

**Design scaled LD to compensate**

- Improvement Action for (2) <u>Probe to bump</u> alignment

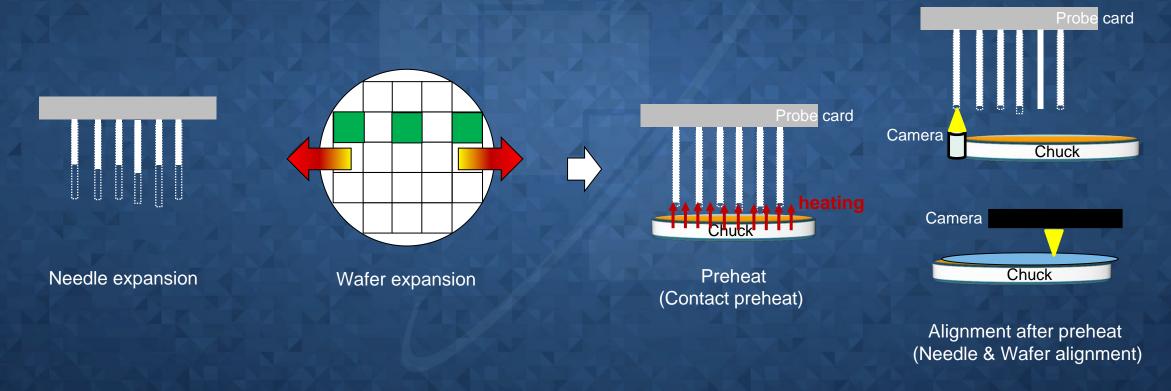

- 3) Execute preheat function and total alignment before testing to make sure needle height and wafer position are stable after thermal expansion.

- Improvement Action for (2) <u>Probe to bump</u> alignment

- 4) Enable more pin alignment function to make sure precise alignment.

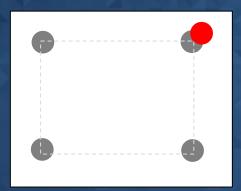

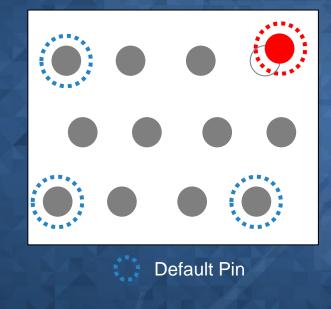

AS IS (4 pin alignment)

If 1 pin shift have Probe Mark Shift Risk

TO BE (> 4 pins alignment) Default Pin Additional Pin

Probe Center  $(\theta)$  = Pin data angle $(\theta)$  + Card angle $(\theta)$  + Offset

- Improvement Action for (2) <u>Probe to bump</u> alignment

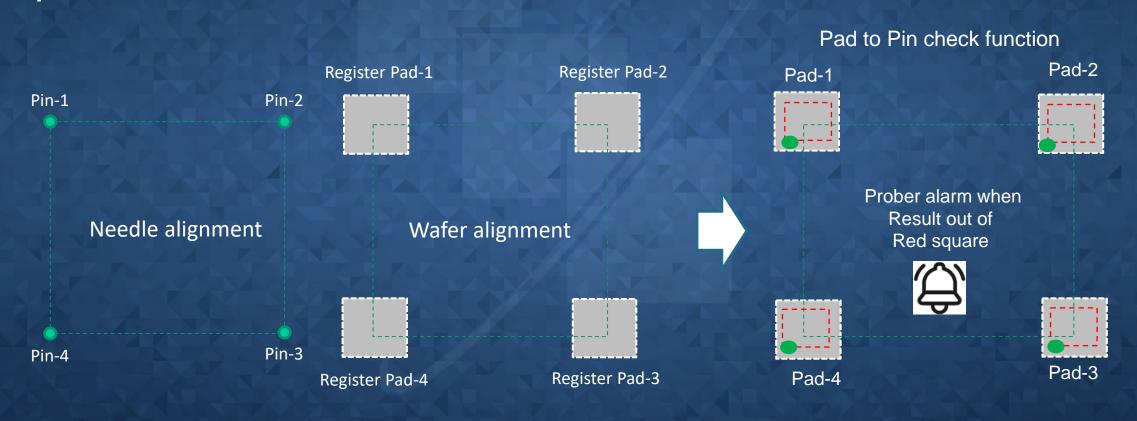

- 5) Enable Pad to Pin check function to forecast contact position and pre-alert before production.

### Summary

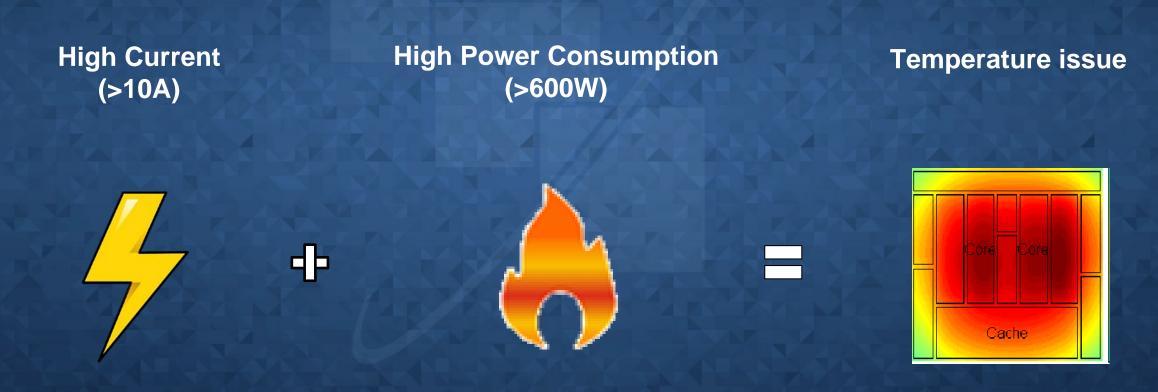

- The demand of HPC chip increase significantly.

- The challenges and improvement actions are studied.

| HPC Characteristics | Challenges                 | Improvement Actions                  |

|---------------------|----------------------------|--------------------------------------|

| Force               | PCB Deformation            | Enhance stiffener structure          |

|                     | Chuck Bending              | Enable 3D offset function            |

| Power               | Tip burnt                  | Hybrid probe                         |

|                     | Temperature control        | Index move optimization              |

|                     |                            | Multiple sensor and control zones    |

| Temperature         | Probe to MLO Pad alignment | Control the scaling of MLO dimension |

|                     |                            | Enlarge MLO Pad size                 |

|                     |                            | Design scaled UD                     |

|                     | Probe to bump alignment    | Constrain probing area               |

|                     |                            | Design scaled LD                     |

|                     |                            | Enable more Pin alignment            |

|                     |                            | Enable Pad to Pin check              |